- 您现在的位置:买卖IC网 > PDF目录378279 > ADC0833CCN (NATIONAL SEMICONDUCTOR CORP) 8-Bit Serial I/O A/D Converter with 4-Channel Multiplexer PDF资料下载

参数资料

| 型号: | ADC0833CCN |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | ADC |

| 英文描述: | 8-Bit Serial I/O A/D Converter with 4-Channel Multiplexer |

| 中文描述: | 4-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP14 |

| 封装: | 0.300 INCH, PLASTIC, DIP-14 |

| 文件页数: | 5/20页 |

| 文件大小: | 316K |

| 代理商: | ADC0833CCN |

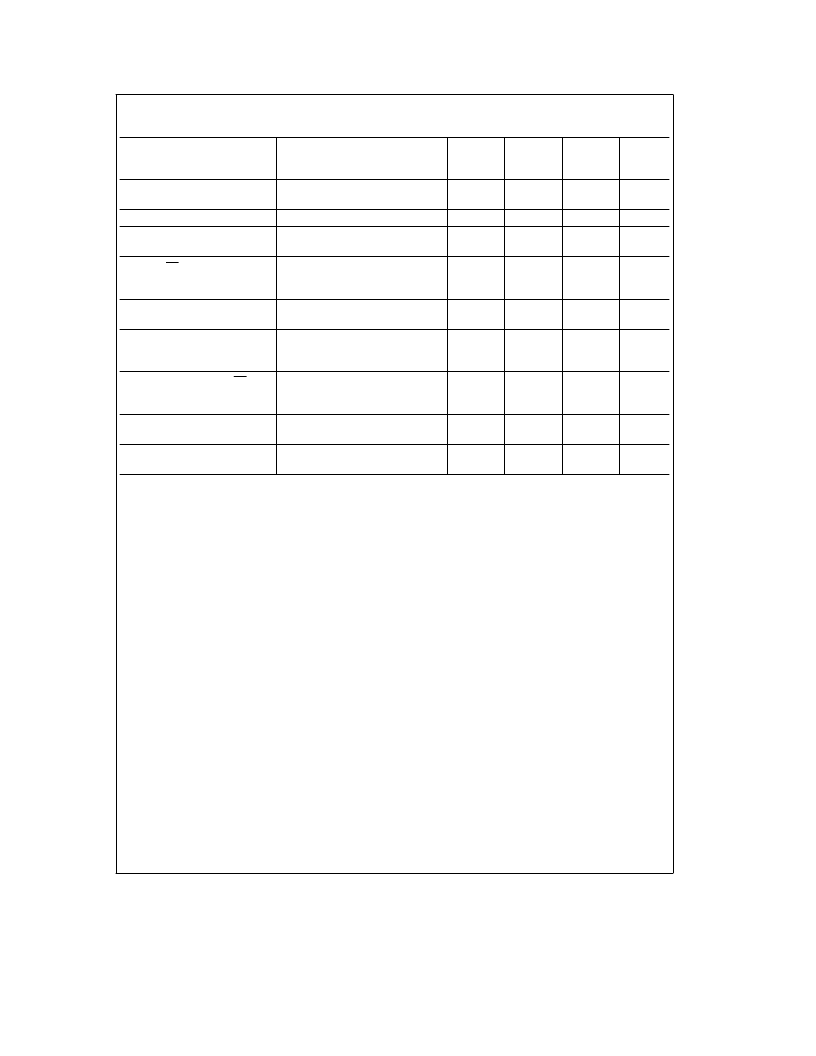

AC Electrical Characteristics

The following specifications apply for V

CC

e

V

a

e

5V and t

r

e

t

f

e

20 ns

unless otherwise specified. These limits apply for T

A

e

T

j

e

25

§

C.

Typ

Tested

Limit

(Note 7)

Design

Limit

(Note 8)

Parameter

Conditions

(Note 6)

Units

f

CLK

, Clock Frequency

Min

Max

10

kHz

kHz

400

T

C

, Conversion Time

Not including MUX Addressing Time

8

1/f

CLK

Clock Duty Cycle (Note 12)

Min

Max

40

60

%

%

t

SET-UP

, CS Falling Edge or

Data Input Valid to CLK

Rising Edge

250

ns

t

HOLD

, Data Input Valid

after CLK Rising Edge

90

ns

t

pd1

, t

pd0

DCLK Falling

Edge to Output Data Valid

(Note 13)

C

L

e

100 pF

Data MSB First

Data LSB First

650

250

1500

600

ns

ns

t

1H

, t

OH

DRising Edge of CS

to Data Output and SARS

Hi-Z

C

L

e

10 pF, R

L

e

10k

C

L

e

100 pF, R

L

e

2k

(see TRI-STATE Test Circuits)

125

250

ns

ns

500

C

IN

, Capacitance of Logic

Input

5

pF

C

OUT

, Capacitance of Logic

Outputs

5

pF

Note 1:

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2:

All voltages are measured with respect to the ground pins.

Note 3:

Internal zener diodes (approx. 7V) are connected from V

a

to GND and V

CC

to GND. The zener at V

a

can operate as a shunt regulator and is connected to

V

CC

via a conventional diode. Since the zener voltage equals the A/D’s breakdown voltage, the diode insures that V

CC

will be below breakdown when the device is

powered from V

a

. Functionality is therefore guaranteed for V

a

operation even though the resultant voltage at V

CC

may exceed the specified Absolute Max. of

6.5V. It is recommended that a resistor be used to limit the max. current into V

a

.

Note 4:

When the input voltage (V

IN

) at any pin exceeds the power supply rails (V

IN

k

V

b

or V

IN

l

V

a

) the absolute value of current at that pin should be limited

to 5 mA or less. The 20 mA package input current limits the number of pins that can exceed the power supply boundaries with a 5 mA current limit to four.

Note 5:

Human body model, 100 pF discharged through a 1.5 k

X

resistor.

Note 6:

Typicals are at 25

§

C and represent most likely parametric norm.

Note 7:

Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 8:

Design limits are guaranteed but not 100% tested. These limits are not used to calculate outgoing quality levels.

Note 9:

See Applications, section 3.0.

Note 10:

For V

IN

(

b

)

t

V

IN

(

a

) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see Block Diagram) which will forward

conduct for analog input voltages one diode drop below ground or one diode drop greater than the V

CC

supply. Be careful, during testing at low V

CC

levels (4.5V),

as high level analog inputs (5V) can cause this input diode to conductDespecially at elevated temperatures, and cause errors for analog inputs near full-scale. The

spec allows 50 mV forward bias of either diode. This means that as long as the analog V

IN

or V

REF

does not exceed the supply voltage by more than 50 mV, the

output code will be correct. To achieve an absolute 0 V

DC

to 5 V

DC

input voltage range will therefore require a minimum supply voltage of 4.950 V

DC

over

temperature variations, initial tolerance and loading.

Note 11:

Leakage current is measured with the clock not switching.

Note 12:

A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of

these limits, the minimum time the clock is high or the minimum time the clock is low must be at least 1

m

s. The maximum time the clock can be high is 60

m

s. The

clocked can be stopped when low so long as the analog input voltage remains stable.

Note 13:

Since data, MSB first, is the output of the comparator used in the successive approximation loop, an additional delay is built in (see Block Diagram) to

allow for comparator response time.

5

相关PDF资料 |

PDF描述 |

|---|---|

| ADC08351 | 8-Bit, 42 MSPS, 40 mW A/D Converter |

| ADC08351CIMTC | 8-Bit, 42 MSPS, 40 mW A/D Converter |

| ADC08351CIMTCX | 8-Bit, 42 MSPS, 40 mW A/D Converter |

| ADC0841 | 8-Bit P Compatible A/D Converter |

| ADC0841BCN | 8-Bit P Compatible A/D Converter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADC0833CCN/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0833CCN/B+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0833CJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0834 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit Serial I/O A/D Converters with Multiplexer Options |

| ADC0834A | 制造商:TI 制造商全称:Texas Instruments 功能描述:A/D PERIPHERALS WITH SERIAL CONTROL |

发布紧急采购,3分钟左右您将得到回复。