- 您现在的位置:买卖IC网 > PDF目录10737 > ADCMP607BCPZ-WP (Analog Devices Inc)IC COMP TTL/CMOS 1CHAN 12-LFCSP PDF资料下载

参数资料

| 型号: | ADCMP607BCPZ-WP |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/16页 |

| 文件大小: | 0K |

| 描述: | IC COMP TTL/CMOS 1CHAN 12-LFCSP |

| 标准包装: | 50 |

| 类型: | 带锁销 |

| 元件数: | 1 |

| 输出类型: | CML,补充型,满摆幅 |

| 电压 - 电源,单路/双路(±): | 2.5 V ~ 5.5 V |

| 电压 - 输入偏移(最小值): | 5mV @ 2.5V |

| 电流 - 输入偏压(最小值): | 5µA @ 2.5V |

| 电流 - 输出(标准): | 50mA |

| 电流 - 静态(最大值): | 1.5mA |

| CMRR, PSRR(标准): | 50dB CMRR,50dB PSRR |

| 传输延迟(最大): | 2.1ns |

| 磁滞: | 100µV |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 12-VFQFN 裸露焊盘,CSP |

| 安装类型: | 表面贴装 |

| 包装: | 托盘 - 晶粒 |

ADCMP606/ADCMP607

Rev. A | Page 7 of 16

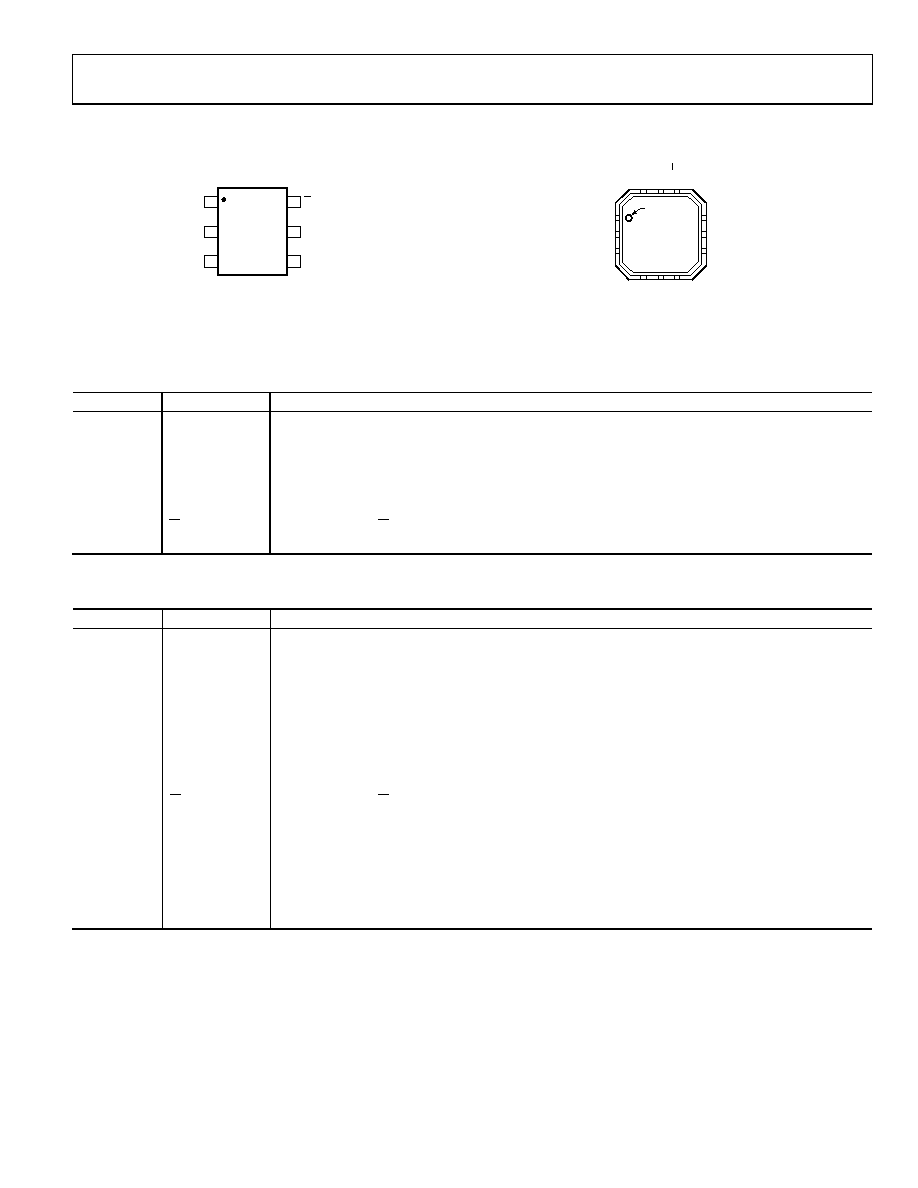

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Q 1

VEE 2

VP 3

Q

6

VCCI/VCCO

5

VN

4

ADCMP606

TOP VIEW

(Not to Scale)

05

91

7-

0

02

PIN 1

INDICATOR

TOP VIEW

(Not to Scale)

ADCMP607

VCCO 1

VCCI 2

VEE 3

V

P

4

V

EE

5

V

N

6

9 VEE

8 LE/HYS

7 SDN

12

Q

11

V

EE

10

Q

0

591

7-

0

03

Figure 3. ADCMP606 Pin Configuration

Figure 4. ADCMP607 Pin Configuration

Table 5. ADCMP606 (6-Lead SC70) Pin Function Descriptions

Pin No.

Mnemonic

Description

1

Q

Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, VP, is greater than

the analog voltage at the inverting input, VN.

2

VEE

Negative Supply Voltage.

3

VP

Noninverting Analog Input.

4

VN

Inverting Analog Input.

5

VCCI/VCCO

Input Section Supply/Output Section Supply. Shared pin.

6

Q

Inverting Output. Q is at logic low if the analog voltage at the noninverting input, VP, is greater than the

analog voltage at the inverting input, VIN.

Table 6. ADCMP607 (12-Lead LFCSP) Pin Function Descriptions

Pin No.

Mnemonic

Description

1

VCCO

Output Section Supply.

2

VCCI

Input Section Supply.

3

VEE

Negative Supply Voltage.

4

VP

Noninverting Analog Input.

5

VEE

Negative Supply Voltage.

6

VN

Inverting Analog Input.

7

SDN

Shutdown. Drive this pin low to shut down the device.

8

LE/HYS

Latch/Hysteresis Control. Bias with resistor or current for hysteresis adjustment; drive low to latch.

9

VEE

Negative Supply Voltage.

10

Q

Inverting Output. Q is at logic low if the analog voltage at the noninverting input, VP, is greater than the

analog voltage at the inverting input, VN, if the comparator is in compare mode.

11

VEE

Negative Supply Voltage.

12

Q

Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, VP, is greater than

the analog voltage at the inverting input, VN, if the comparator is in compare mode.

Heat Sink

Paddle

VEE

The metallic back surface of the package is electrically connected to VEE. It can be left floating because

Pin 3, Pin 5, Pin 9, and Pin 11 provide adequate electrical connection. It can also be soldered to the

application board if improved thermal and/or mechanical stability is desired.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-JNR-MY-F4 | CONVERTER MOD DC/DC 7.5V 50W |

| VI-BWY-MW-B1 | CONVERTER MOD DC/DC 3.3V 66W |

| VI-JNR-MY-F2 | CONVERTER MOD DC/DC 7.5V 50W |

| VI-BWW-MY-B1 | CONVERTER MOD DC/DC 5.5V 50W |

| VI-JNR-MY-F1 | CONVERTER MOD DC/DC 7.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADCMP608 | 制造商:AD 制造商全称:Analog Devices 功能描述:Rail-to-Rail, Fast, Low Power 2.5 V to 5.5 V, Single-Supply TTL/CMOS Comparator |

| ADCMP608_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:Rail-to-Rail, Fast, Low Power 2.5 V to 5.5 V, Single-Supply TTL/CMOS Comparator |

| ADCMP608BKSZ-R2 | 功能描述:IC COMP TTL/CMOS R-R SGL SC70-6 RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:25 系列:- 类型:带电压基准 元件数:4 输出类型:CMOS,开路漏极,TTL 电压 - 电源,单路/双路(±):2 V ~ 11 V,±1 V ~ 5.5 V 电压 - 输入偏移(最小值):10mV @ 5V 电流 - 输入偏压(最小值):- 电流 - 输出(标准):0.015mA @ 5V 电流 - 静态(最大值):8.5µA CMRR, PSRR(标准):80dB CMRR,80dB PSRR 传输延迟(最大):12µs 磁滞:50mV 工作温度:0°C ~ 70°C 封装/外壳:16-DIP(0.300",7.62mm) 安装类型:通孔 包装:管件 |

| ADCMP608BKSZ-REEL | 制造商:AD 制造商全称:Analog Devices 功能描述:Rail-to-Rail, Fast, Low Power 2.5 V to 5.5 V, Single-Supply TTL/CMOS Comparator |

| ADCMP608BKSZ-REEL7 | 功能描述:IC COMPARATOR TTL/CMOS SC70-6 RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:1 系列:- 类型:通用 元件数:1 输出类型:CMOS,开路集电极,TTL 电压 - 电源,单路/双路(±):2.7 V ~ 5.5 V 电压 - 输入偏移(最小值):7mV @ 5V 电流 - 输入偏压(最小值):0.25µA @ 5V 电流 - 输出(标准):84mA @ 5V 电流 - 静态(最大值):120µA CMRR, PSRR(标准):- 传输延迟(最大):600ns 磁滞:- 工作温度:-40°C ~ 85°C 封装/外壳:SC-74A,SOT-753 安装类型:表面贴装 包装:剪切带 (CT) 产品目录页面:1268 (CN2011-ZH PDF) 其它名称:*LMV331M5*LMV331M5/NOPBLMV331M5CT |

发布紧急采购,3分钟左右您将得到回复。