- 您现在的位置:买卖IC网 > PDF目录9103 > ADF4154BRU-REEL7 (Analog Devices Inc)IC FRACTION-N FREQ SYNTH 16TSSOP PDF资料下载

参数资料

| 型号: | ADF4154BRU-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/24页 |

| 文件大小: | 0K |

| 描述: | IC FRACTION-N FREQ SYNTH 16TSSOP |

| 标准包装: | 1,000 |

| 类型: | 分数 N 合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 4GHz |

| 除法器/乘法器: | 无/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-ADF4154EBZ1-ND - BOARD EVALUATION FOR ADF4154EB1 |

Data Sheet

ADF4154

Rev. C | Page 19 of 24

bandwidth can lead to notable spurious signals, which cannot

be reduced significantly by the loop filter.

Using the fast-lock feature can achieve the same fast-lock time

as the noise and spur register, but with the advantage of lower

spurious signals because the final loop bandwidth is reduced by

a quarter.

FAST-LOCK TIMER AND REGISTER SEQUENCES

If the fast-lock mode is used, a timer value needs to be loaded

into the PLL to determine the time spent in wide bandwidth

mode.

When the load control bit is set to 1, the timer value is loaded

via the 12-bit modulus value. To use fast lock, the PLL must be

written to in the following sequence:

1. Load the R-divider register with DB23 = 1 and the chosen

fast-lock timer value (DB13 to DB2) instead of the

modulus. Note that the duration that the PLL remains in

wide bandwidth is equal to the fast-lock timer/fPFD.

2. Load the noise and spur register.

3. Load the control register.

4. Load the R-divider register with DB23 = 0 and MUXOUT

= 110 (DB22 to DB20). This sets the fast-lock switch to

appear at the MUXOUT pin. All the other needed

parameters, including the modulus, also need to be loaded.

5. Load the N-divider register, including fast lock = 1 (DB23),

to activate fast-lock mode.

After this procedure is complete, the user need only repeat

Step 5 to invoke fast lock for subsequent frequency jumps.

FAST LOCK: AN EXAMPLE

If a PLL has reference frequencies of 13 MHz and fPFD = 13 MHz

and a required lock time of 50 s, the PLL is set to wide bandwidth

for 40 s.

If the time period set for the wide bandwidth is 40 s, then

Fast-Lock Timer Value = Time in Wide Bandwidth × fPFD

Fast-Lock Timer Value = 40 s × 13 MHz = 520

Therefore, 520 must be loaded into the R-divider register in

Step 1 of the sequence described in the Fast-Lock Timer and

Register Sequences section.

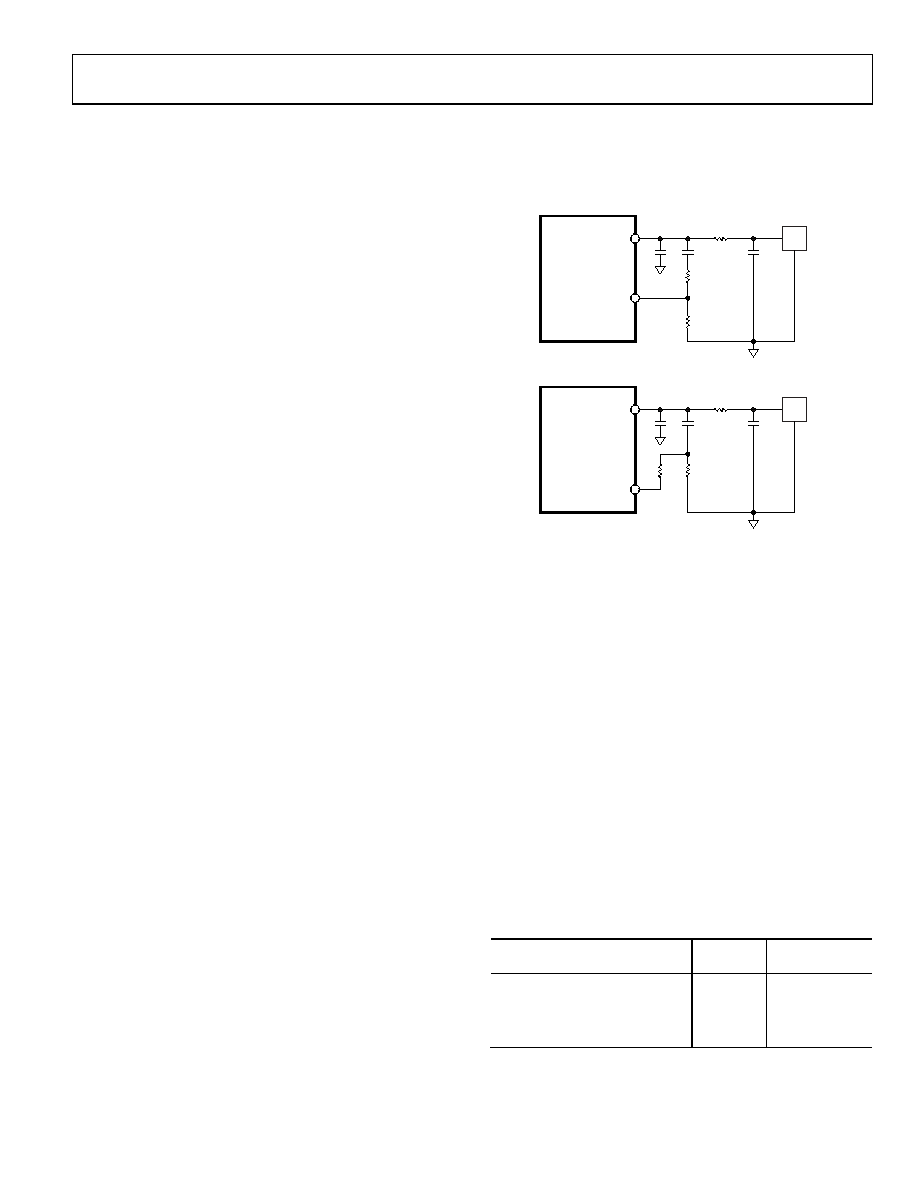

FAST LOCK: LOOP FILTER TOPOLOGY

To use fast-lock mode, an extra connection from the PLL to the

loop filter is needed. The damping resistor in the loop filter

must be reduced to of its value while in wide bandwidth

mode. This is required because the charge pump current is

increased by 16 while in wide bandwidth mode, and stability

must be ensured. During fast lock, the MUXOUT pin is shorted

to ground (the fast-lock switch must be programmed to appear

at the MUXOUT pin). The following two topologies can be used:

Divide the damping resistor (R1) into two values (R1 and

R1A) that have a ratio of 1:3 (see Figure 19).

Connect an extra resistor (R1A) directly from MUXOUT,

as shown in Figure 19. The extra resistor must be chosen

such that the parallel combination of an extra resistor and

the damping resistor (R1) is reduced to of the original

value of R1 (see Figure 20).

ADF4154

CP

MUXOUT

C1

C2

R2

R1

R1A

C3

VCO

04833-

029

Figure 19. Fast-Lock Loop Filter Topology—Topology 1

ADF4154

CP

MUXOUT

C1

C2

R2

R1

R1A

C3

VCO

04833-

030

Figure 20. Fast-Lock Loop Filter Topology—Topology 2

SPUR MECHANISMS

The following section describes three spur mechanisms that can

arise when using a fractional-N synthesizer and how to minimize

them in the ADF4154.

Fractional Spurs

The fractional interpolator in the ADF4154 is a third-order Σ-Δ

modulator (SDM) with a modulus MOD that is programmable

to an integer value between 2 and 4095. In low spur mode

(dither enabled), the minimum allowed value of MOD is 50.

The SDM is clocked at the PFD reference rate (fPFD) that allows

PLL output frequencies to be synthesized at a channel step

resolution of fPFD/MOD.

In low noise mode and low noise and spur mode (dither off),

the quantization noise from the Σ-Δ modulator appears as frac-

tional spurs. The interval between spurs is fPFD/L, where L is the

repeat length of the code sequence in the digital Σ-Δ modulator.

For the third-order modulator used in the ADF4154, the repeat

length depends on the value of MOD, as shown in Table 11.

Table 11. Fractional Spurs with Dither Off

Condition (Dither Off)

Repeat

Length

Spur Interval

If MOD is divisible by 2, but not 3

2 × MOD

Channel step/2

If MOD is divisible by 3, but not 2

3 × MOD

Channel step/3

If MOD is divisible by 6

6 × MOD

Channel step/6

Otherwise

MOD

Channel step

相关PDF资料 |

PDF描述 |

|---|---|

| MS3450L28-11PW | CONN RCPT 22POS WALL MNT W/PINS |

| X9317UP-2.7 | IC XDCP 100TAP 50K 3-WIRE 8-DIP |

| X9317TV8T1 | IC XDCP 100TAP 100K 3WIRE 8TSSOP |

| X9317TV8IT2 | IC XDCP 100TAP 100K 3WIRE 8TSSOP |

| MS3450L28-11P | CONN RCPT 22POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4154BRUZ | 功能描述:IC FRAC-N FREQ SYNTH 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4154BRUZ-RL | 功能描述:IC FRACTION-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4154BRUZ-RL7 | 功能描述:IC FRACTION-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4155BCPZ | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:* PLL:是 输入:LVDS,LVPECL 输出:时钟 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/无 频率 - 最大值:4GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-WFQFN 裸露焊盘,CSP 供应商器件封装:24-LFCSP-WQ(4x4) 标准包装:1 |

| ADF4155BCPZ-RL7 | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:有效 类型:* PLL:是 输入:LVDS,LVPECL 输出:时钟 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/无 频率 - 最大值:4GHz 分频器/倍频器:是/是 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-WFQFN 裸露焊盘,CSP 供应商器件封装:24-LFCSP-WQ(4x4) 标准包装:1,500 |

发布紧急采购,3分钟左右您将得到回复。