- 您现在的位置:买卖IC网 > PDF目录9093 > ADF4158CCPZ-RL7 (Analog Devices Inc)IC FRACTION N FREQ SYNT 24LFCSP PDF资料下载

参数资料

| 型号: | ADF4158CCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/36页 |

| 文件大小: | 0K |

| 描述: | IC FRACTION N FREQ SYNT 24LFCSP |

| 标准包装: | 1,500 |

| 类型: | 分数 N 合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 6.1GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 24-LFCSP-WQ(4x4) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

ADF4158

Rev. G | Page 21 of 36

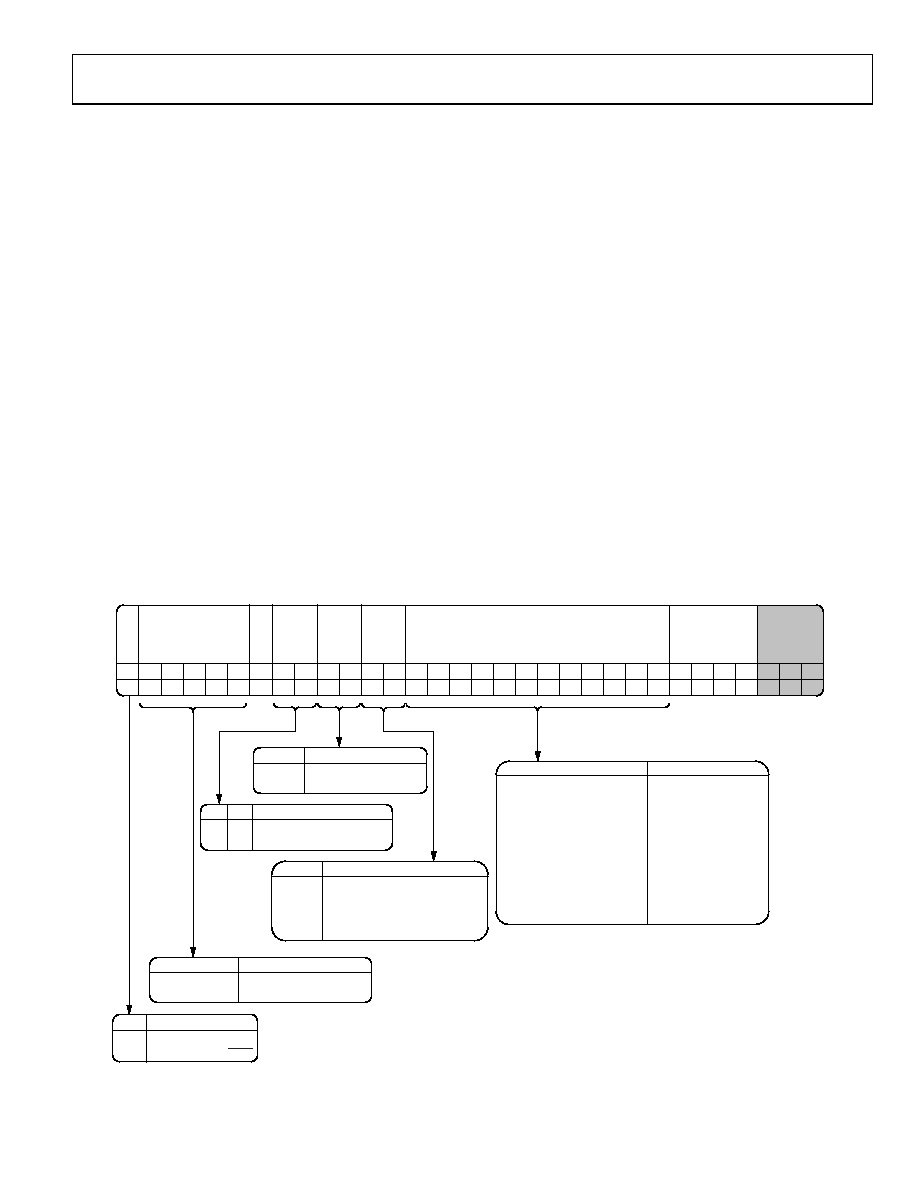

TEST REGISTER (R4) MAP

With Register R4 DB[2:0] set to [1, 0, 0], the on-chip test

register (R4) is programmed as shown in Figure 27.

LE SEL

In some applications, it is necessary to synchronize LE with

the reference signal. To do this, DB31 should be set to 1.

Synchronization is done internally on the part.

Σ-Δ Modulator Mode

To completely disable the Σ-Δ modulator, set Bits DB[30:26] to

0b01110, which puts the ADF4158 into integer-N mode, and

the channel spacing becomes equal to the PFD frequency. Both

the 12-bit MSB fractional value (Register R0, DB[14:3]) and the

13-bit LSB fractional value (Register R1, DB[27:15]) must be set

to 0. After writing to Register 4, Register 3 must be written to twice

to trigger a counter reset. (That is, write Register 3 with DB3 = 1,

and then write Register 3 with DB3 = 0.)

All features driven by the Σ-Δ modulator are disabled, such as

ramping, PSK, FSK, and phase adjust.

Disabling the Σ-Δ modulator also removes the fixed + (fPFD/226)

offset on the VCO output.

For normal operation, set these bits to 0b00000.

Reserved Bits

All reserved bits should be set to 0 for normal operation.

Negative Bleed Current

Setting Bits DB[24:23] to 11 turns on the constant negative

bleed current. This ensures that the charge pump operates out

of the dead zone. Thus, the phase noise is not degraded and the

level of spurs is lower. Enabling constant negative bleed current

is particularly important on channels close to multiple PFD

frequencies. Refer to the AN-1154 Application Note for more

information on the negative bleed current. When using negative

bleed current, readback to MUXOUT must be disabled.

Readback to MUXOUT

DB[22:21] enable or disable the readback to MUXOUT function.

This function allows reading back the synthesizer’s frequency at

the moment of interrupt. When using readback to MUXOUT,

negative bleed current must be off.

Clock Divider (DIV) Mode

Bits DB[20:19] are used to enable ramp divider mode or fast

lock divider mode. If neither is being used, set these bits to 0b00.

12-Bit CLK2 Divider Value

Bits DB[18:7] program the clock divider (the CLK2 timer) when

the part operates in ramp mode (see the Timeout Interval section).

The CLK2 timer also determines how long the loop remains in

wideband mode when fast lock mode is used (see the Fast Lock

Mode section).

DB31

12-BIT CLK2 DIVIDER VALUE

Σ- MODULATOR

MODE

R

ESER

VED

LE

S

E

L

RESERVED

CONTROL

BITS

DB30 DB29 DB28 DB27 DB26 DB25

DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

LS1

S5

S4

S3

S2

S1

0

R2R1C2C1

D12

D11 D10

D9D8D7

D6D5D4D3D2

D1

C3(1) C2(0) C1(0)

D12

D11

.......... D2

D1

CLOCK DIVIDER VALUE

0

.

1

0

.

1

0

1

.

0

1

0

1

0

1

.

0

1

0

1

0

1

2

3

.

4092

4093

4094

4095

..........

CK2 CK1 CLOCK DIVIDER MODE

00

CLOCK DIVIDER OFF

01

FAST-LOCK DIVIDER

10

RESERVED

1

RAMP DIVIDER

00

0

CLK

DIV

MODE

READ-

BACK

TO

MUXOUT

08

728

-11

5

DB24 DB23

NB2 NB1

NEG

BLEED

CURR-

ENT

R2

READBACK TO MUXOUT

0

DISABLED

1

ENABLED

R1

0

NB2

NEGATIVE BLEED CURRENT

0OFF

1

ON

NB1

0

1

LS1

LE SEL

0

1

S2

S3

S4

S5

S1

Σ- MODULATOR MODE

0

NORMAL OPERATION

1

0

00

1

010

DISABLED WHEN FRAC = 0

LE FROM PIN

LE SYNCH WITH REFIN

Figure 27. Test Register (R4) Map

相关PDF资料 |

PDF描述 |

|---|---|

| X9409WV24-2.7T1 | IC XDCP QUAD 64-TAP 10K 24-TSSOP |

| X9409WS24T1 | IC XDCP QUAD 64-TAP 10K 24-SOIC |

| VE-B5Z-MU-S | CONVERTER MOD DC/DC 2V 80W |

| X9409WS24IT1 | IC XDCP QUAD 64-TAP 10K 24-SOIC |

| VE-B5Y-MU-S | CONVERTER MOD DC/DC 3.3V 132W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4158WCCPZ | 功能描述:IC FRAC-N FREQ SYNTH 24LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:在售 类型:分数 N 合成器(RF) PLL:是 输入:CMOS,TTL 输出:时钟 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/无 频率 - 最大值:6.1GHz 分频器/倍频器:是/是 电压 - 电源:2.7 V ~ 3.3 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-WFQFN 裸露焊盘 供应商器件封装:24-LFCSP-WQ(4x4) 标准包装:1 |

| ADF4158WCCPZ-RL7 | 功能描述:IC FRAC-N FREQ SYNTH 24LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4159 | 制造商:AD 制造商全称:Analog Devices 功能描述:Direct Modulation/Fast Waveform Generating, 13 GHz, Fractional-N Frequency Synthesizer |

| ADF4159CCPZ | 制造商:Analog Devices 功能描述:Fractional-N Frequency Synthesizer 24-Pin LFCSP EP Tray 制造商:Analog Devices 功能描述:DIRECT MODULATION/FAST WAVEFORM GENERATING, 13 GHZ, FRACTION - Trays 制造商:Analog Devices 功能描述:IC PLL FREQ SYNTHESIZER 24LFCSP 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL |

| ADF4159CCPZ-RL7 | 制造商:Analog Devices 功能描述:Fractional-N Frequency Synthesizer 24-Pin LFCSP EP T/R 制造商:Analog Devices 功能描述:13GHZ FAST RAMP DIRECT MOD FRAC N PLL - Tape and Reel 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL |

发布紧急采购,3分钟左右您将得到回复。