- 您现在的位置:买卖IC网 > PDF目录1989 > ADF4158WCCPZ-RL7 (Analog Devices Inc)IC FRAC-N FREQ SYNTH 24LFCSP PDF资料下载

参数资料

| 型号: | ADF4158WCCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/36页 |

| 文件大小: | 0K |

| 描述: | IC FRAC-N FREQ SYNTH 24LFCSP |

| 标准包装: | 1,500 |

| 类型: | 分数 N 合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 6.1GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 24-LFCSP-WQ(4x4) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

ADF4158

Rev. G | Page 29 of 36

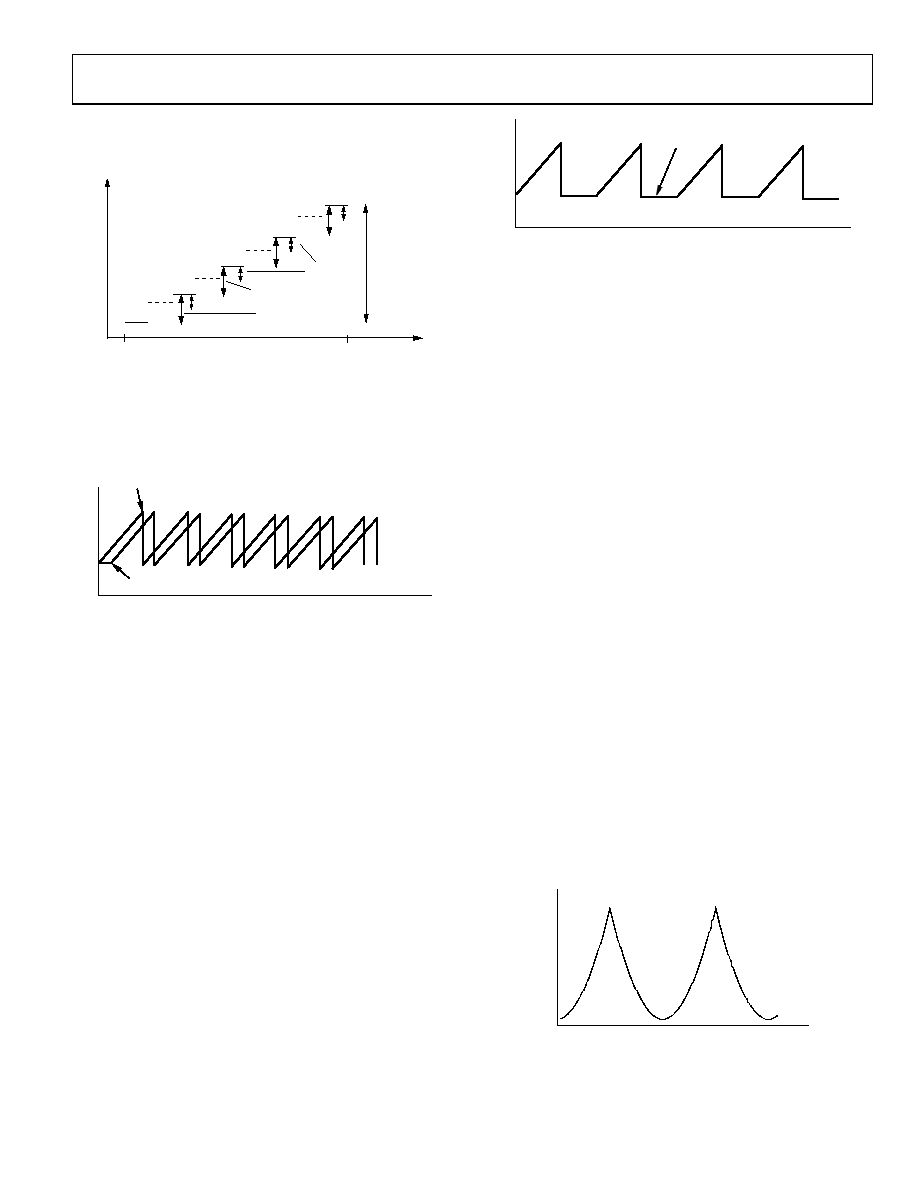

An example of ramp with FSK on the top of it is shown in

Figure 37. Eventually, the ramp must be activated as described

in Activating the Ramp section.

08728-

025

FR

E

Q

U

E

N

C

Y

0RAMP END

F

R

EQ

U

EN

C

Y

SW

EEP

FSK SHIFT

TIME

LFM STEP =

FREQUENCY

SWEEP/NUMBER

OF STEPS

Figure 37. Combined FSK and LFM Waveform (N Corresponds to the

Number of LFM Steps)

Delayed Start

A delayed start can be used with two different parts to control

the start time. The idea of delayed start is shown in Figure 38.

FR

E

Q

U

E

N

C

Y

TIME

RAMP WITH

DELAYED START

RAMP WITHOUT

DELAYED START

08

728

-12

6

Figure 38. Delayed Start of Sawtooth Ramp

Example

For example, to program a delayed start with two different parts

to control the start time,

1.

Set DB15 in Register R7 to 1 to enable the delayed start of

ramp option.

2.

Set Bit DB16 in Register R7 to 0 and the 12-bit delay start

word (DB[14:3] in Register R7) to 125 to delay the ramp on

the first part is delayed by 5 μs, fPFD = 25 MHz. The delay is

calculated as follows:

Delay = tPFD × Delay Start Word

= 40 ns × 125 = 5 μs

3.

Set Bit DB16 in Register R7 to 1 and the 12-bit delay start

word (DB[14:3] in Register R7) to 125 to delay the ramp

on the second part is delayed by 125 μs. Use the following

formula for calculating the delay:

Delay = tPFD × CLK1 × Delay Start Word

= 40 ns × 25 × 125 = 125 μs

Eventually, the ramp must be activated as described in

Delay Between Ramps

This feature adds a delay between bursts in ramp. Figure 39

shows a delay between ramps in sawtooth mode.

FR

E

Q

U

E

N

C

Y

TIME

DELAY

08

72

8-

02

8

Figure 39. Delay Between Ramps for Sawtooth Mode

Example

For example, to add a delay between bursts in a ramp,

1.

Set DB17 in Register R7 to 1 to enable delay between

ramps option.

2.

Set Bit DB16 in Register R7 to 0 and the 12-bit delay start

word (DB[14:3] in Register R7) to 125 to delay the ramp

by 5 μs, fPFD = 25 MHz. The delay is calculated as follows:

Delay = tPFD × Delay Start Word

= 40 ns × 125 = 5 μs

If a longer delay is needed, for example, 125 μs, Bit DB16

in Register R7 should be set to 1 and the 12-bit delay start

word (DB[14:3] in Register R7) should be set to 125. The

delay is calculated as follows

Delay = tPFD × CLK1 × Delay Start Word

= 40 ns × 25 × 125 = 125 μs

There is also a possibility to activate fast-lock operation for the

first period of delay. This is done by setting Bit DB18 in Register R7

to 1. This feature is useful for sawtooth ramps to mitigate the

frequency overshoot on the transition from one sawtooth to the

next. Eventually, the ramp must be activated as described in

Nonlinear Ramp Mode

The ADF4158 is capable of generating a parabolic ramp. The

output frequency is generated according to the following

equation:

fOUT(n + 1) = fOUT(n) + n × fDEV

(16)

where:

fOUT is output frequency.

n is step number.

fDEV is frequency deviation.

FR

E

Q

U

E

N

C

Y

TIME

087

28-

029

Figure 40. Parabolic Ramp

相关PDF资料 |

PDF描述 |

|---|---|

| ADF4193BCPZ-RL7 | IC PLL FREQ SYNTHESIZER 32LFCSP |

| ADF4206BRUZ-RL | IC PLL FREQ SYNTHESIZER 16TSSOP |

| ADF4212LBRUZ | IC PLL FREQ SYNTHESIZER 20TSSOP |

| ADF4213BCPZ-RL | IC PLL FREQ SYNTHESIZER 20LFCSP |

| ADF4216BRUZ-RL | IC PLL FREQ SYNTHESIZER 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4159 | 制造商:AD 制造商全称:Analog Devices 功能描述:Direct Modulation/Fast Waveform Generating, 13 GHz, Fractional-N Frequency Synthesizer |

| ADF4159CCPZ | 制造商:Analog Devices 功能描述:Fractional-N Frequency Synthesizer 24-Pin LFCSP EP Tray 制造商:Analog Devices 功能描述:DIRECT MODULATION/FAST WAVEFORM GENERATING, 13 GHZ, FRACTION - Trays 制造商:Analog Devices 功能描述:IC PLL FREQ SYNTHESIZER 24LFCSP 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL |

| ADF4159CCPZ-RL7 | 制造商:Analog Devices 功能描述:Fractional-N Frequency Synthesizer 24-Pin LFCSP EP T/R 制造商:Analog Devices 功能描述:13GHZ FAST RAMP DIRECT MOD FRAC N PLL - Tape and Reel 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL |

| ADF4159WCCPZ | 功能描述:13GHZ FAST RAMP DIRECT MOD FRAC 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:在售 类型:频率合成器 PLL:是 输入:CMOS,TTL 输出:CMOS 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/无 频率 - 最大值:13GHz 分频器/倍频器:是/无 电压 - 电源:1.62 V ~ 3.45 V 工作温度:-40°C ~ 125°C(TA) 安装类型:表面贴装 封装/外壳:24-WFQFN 裸露焊盘,CSP 供应商器件封装:24-LFCSP-WQ(4x4) 标准包装:1 |

| ADF4159WCCPZ-RL7 | 功能描述:13GHZ FAST RAMP DIRECT MOD FRAC 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 类型:频率合成器 PLL:是 输入:CMOS,TTL 输出:CMOS 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/无 频率 - 最大值:13GHz 分频器/倍频器:是/无 电压 - 电源:1.62 V ~ 3.45 V 工作温度:-40°C ~ 125°C(TA) 安装类型:表面贴装 封装/外壳:24-WFQFN 裸露焊盘,CSP 供应商器件封装:24-LFCSP-WQ(4x4) 标准包装:1,500 |

发布紧急采购,3分钟左右您将得到回复。