- 您现在的位置:买卖IC网 > PDF目录1989 > ADF4193BCPZ-RL7 (Analog Devices Inc)IC PLL FREQ SYNTHESIZER 32LFCSP PDF资料下载

参数资料

| 型号: | ADF4193BCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/32页 |

| 文件大小: | 0K |

| 描述: | IC PLL FREQ SYNTHESIZER 32LFCSP |

| 标准包装: | 1,500 |

| 类型: | 时钟/频率合成器,RF |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 3.5GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-ADF4193EBZ2-ND - BOARD EVALUATION EB2 FOR ADF4193 EVAL-ADF4193EBZ1-ND - BOARD EVALUATION EB1 FOR ADF4193 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页

Data Sheet

ADF4193

Rev. F | Page 9 of 32

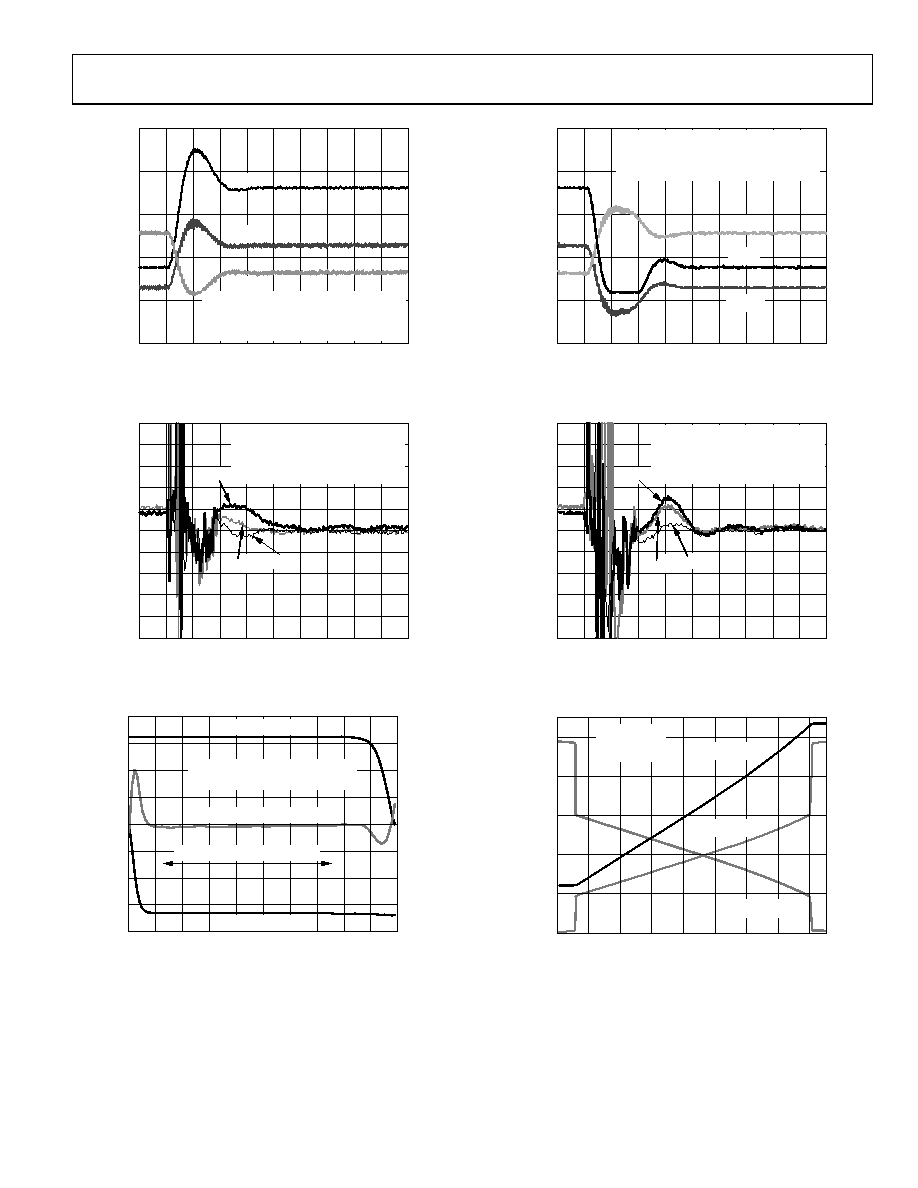

05328-040

TIME (

s)

(V)

–1

0

1

2

3

4

5

9

8

7

6

5

4

3

2

1

0

VTUNE

CPOUT+

CPOUT–

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 4

s.

Figure 10. VTUNE Settling Transient for a 75 MHz Jump from 1818 MHz to

1893 MHz with Sirenza 1843T VCO

05328-008

TIME (

s)

PHASE

ERROR

(Degrees)

–5

0

5

10

15

20

25

30

35

40

–50

50

40

30

20

10

0

–10

–20

–30

–40

45

+25

°C

+85

°C

–40

°C

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

PEAK PHASE ERROR < 5

° @ 17.8s

Figure 11. Phase Settling Transient for a 75 MHz Jump from 1818 MHz to

1893 MHz (VTUNE 1.8 V to 3.7 V with Sirenza 1843T VCO)

05328-

012

CPOUT + / CPOUT – VOLTAGE (V)

I CP

(

mA)

M

IS

M

AT

CH

(

%)

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

–8

–6

–4

–2

0

2

4

6

8

–2.0

–1.5

–1.0

–0.5

0

0.5

1.0

1.5

2.0

5.0

ICPOUT + P, ICPOUT – P

CHARGE PUMP MISMATCH (%)

NORMAL OPERATING RANGE

ICPOUT + N, ICPOUT – N

IUP = | ICPOUT + P | + | ICPOUT – N |

IDOWN = | ICPOUT – P | + | ICPOUT + N |

Figure 12. Differential Charge Pump Output Compliance Range and

Charge Pump Mismatch with VP1 = VP2 = 5 V

05328-041

TIME (

s)

(V)

–1

0

1

2

3

4

5

9

8

7

6

5

4

3

2

1

0

VTUNE

CPOUT–

CPOUT+

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 5

s.

Figure 13. VTUNE Settling Transient for a 75 MHz Jump Down from 1893 MHz to

1818 MHz, the Bottom of the Allowed Tuning Range with the Sirenza 1843T VCO

05328-009

TIME (

s)

PHASE

ERROR

(Degrees)

–5

0

5

10

15

20

25

30

35

40

–50

50

40

30

20

10

0

–10

–20

–30

–40

45

+25

°C

+85

°C

–40

°C

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

PEAK PHASE ERROR < 5

° @ 19.2s

Figure 14. Phase Settling Transient for a 75 MHz Jump from 1893 MHz to

1818 MHz (VTUNE = 3.7 V to 1.8 V with Sirenza 1843T VCO)�

05328-

013

FREQUENCY (MHz)

(V)

1780

1800

1820

1840

1860

1880

1900

1920

1940

0

2

1

3

4

5

VP1 = VP2 = 5V

VP3 = 5.5V

VCMR = 3.3V

CPOUT– (= AIN–)

AOUT (= VTUNE)

CPOUT+ (= AIN+)

Figure 15. Tuning Range with a Sirenza 1843T VCO and a 5.5 V Differential

Amplifier Power Supply Voltage

相关PDF资料 |

PDF描述 |

|---|---|

| ADF4206BRUZ-RL | IC PLL FREQ SYNTHESIZER 16TSSOP |

| ADF4212LBRUZ | IC PLL FREQ SYNTHESIZER 20TSSOP |

| ADF4213BCPZ-RL | IC PLL FREQ SYNTHESIZER 20LFCSP |

| ADF4216BRUZ-RL | IC PLL FREQ SYNTHESIZER 20TSSOP |

| ADF4218LBRUZ | IC PLL FREQ SYNTHESIZER 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4193SP1BCPZ | 制造商:Analog Devices 功能描述: |

| ADF4193SP1BCPZ-RL7 | 制造商:Analog Devices 功能描述: |

| ADF4193SP2BCPZ-RL7 | 制造商:Analog Devices 功能描述: |

| ADF4193WCCPZ-RL7 | 功能描述:IC PLL FREQ SYNTHESIZER 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ADF4196 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Phase Noise, Fast Settling, 6 GHz |

发布紧急采购,3分钟左右您将得到回复。