参数资料

| 型号: | ADMC401BSTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 58/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 8CH 12BIT MOTCTRL 144LQFP |

| 标准包装: | 1 |

| 系列: | 电机控制 |

| 类型: | 定点 |

| 接口: | 串行端口 |

| 时钟速率: | 26MHz |

| 非易失内存: | ROM(6 kB) |

| 芯片上RAM: | 8kB |

| 电压 - 输入/输出: | 5.00V |

| 电压 - 核心: | 5.00V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页

ADMC401

–7–

REV. B

Parameter

Min

Max

Unit

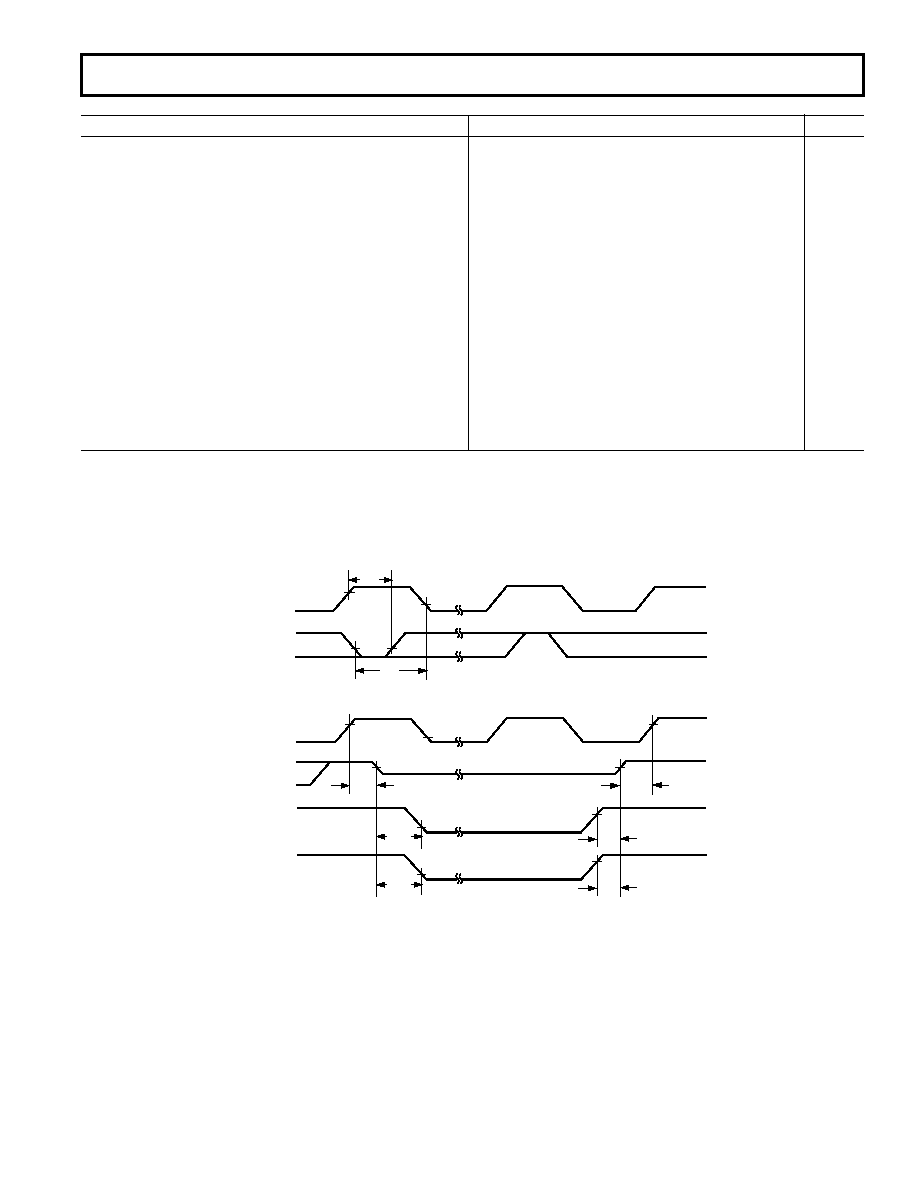

Bus Request/Grant

Timing Requirements:

t

BH

BR Hold after CLKOUT High1

0.25t

CK +2

ns

t

BS

BR Setup before CLKOUT Low1

0.25t

CK + 17

ns

Switching Characteristics:

t

SD

CLKOUT High to

DMS, PMS, BMS,

0.25t

CK + 10

ns

RD, WR Disable

t

SDB

DMS, PMS, BMS, RD, WR

Disable to

BG Low

0

ns

t

SE

BG High to DMS, PMS, BMS,

RD, WR Enable

0

ns

t

SEC

DMS, PMS, BMS, RD, WR

Enable to CLKOUT High

0.25t

CK – 7

ns

t

SDBH

DMS, PMS, BMS, RD, WR

Disable to

BGH Low2

0ns

t

SEH

BGH High to DMS, PMS, BMS,

RD, WR Enable2

0ns

NOTES

1

BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized

on the following cycle. Refer to the ADSP-2100 Family User’s Manual, Third Edition for

BR/BG cycle relationships.

2

BGH is asserted when the bus is granted and the processor requires control of the bus to continue.

BR

CLKOUT

PMS, DMS

BMS, RD

WR

BG

CLKOUT

BGH

tBH

tBS

tSD

tSDB

tSDBH

tSEH

tSE

tSEC

Figure 3. Bus Request–Bus Grant

相关PDF资料 |

PDF描述 |

|---|---|

| ADN2850BCPZ25-RL7 | IC DGTL RHEO DL 25K 9BIT16LFCSP |

| ADN2860ACPZ250-RL7 | IC POT DGTL 3CH 250K 24-LFCSP |

| ADN4600ACPZ | IC CROSSPOINT SWITCH 8X8 64LFCSP |

| ADN4604ASVZ-RL | IC CROSSPOINT SWIT 16X16 100TQFP |

| ADN4605ABPZ | IC CROSSPOINT SWITCH 352BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADMC401BSTZKL1 | 制造商:Analog Devices 功能描述: |

| ADMC401-PB | 制造商:AD 制造商全称:Analog Devices 功能描述:Single-Chip, DSP-Based High Performance Motor Controller |

| ADMCF326 | 制造商:AD 制造商全称:Analog Devices 功能描述:28-Lead Flash Memory DSP Motor Controller |

| ADMCF326BN | 制造商:Analog Devices 功能描述: |

| ADMCF326BR | 制造商:AD 制造商全称:Analog Devices 功能描述:28-Lead Flash Memory DSP Motor Controller |

发布紧急采购,3分钟左右您将得到回复。