参数资料

| 型号: | ADN2805ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/16页 |

| 文件大小: | 0K |

| 描述: | IC CLK/DATA REC 1.25GBPS 32LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

ADN2805

Data Sheet

Rev. B | Page 12 of 16

FUNCTIONAL DESCRIPTION

FREQUENCY ACQUISITION

The ADN2805 acquires frequency from the data at 1.25 Gbps.

The lock detector circuit compares the frequency of the VCO

and the frequency of the incoming data. When these frequen-

cies differ by more than 1000 ppm, LOL asserts. This initiates a

frequency acquisition cycle. An on-chip frequency-locked loop

(FLL) forces the frequency of the VCO to be approximately

equal to the frequency of the incoming data. LOL is deasserted

once the VCO frequency is within 250 ppm of the data frequency.

When LOL deasserts, the FLL turns off. The PLL/DLL pulls in

the VCO frequency until the VCO frequency equals the data

frequency.

The frequency loop requires a single external capacitor between

CF1 and CF2, Pin 15 and Pin 14. A 0.47 μF ± 20%, X7R ceramic

chip capacitor with <10 nA leakage current is recommended.

Calculate the leakage current of the capacitor by dividing the

maximum voltage across the 0.47 μF capacitor, ~3 V, by the

insulation resistance of the capacitor. The insulation resistance

of the 0.47 μF capacitor should be greater than 300 MΩ.

INPUT BUFFER

The input buffer has differential inputs (PIN/NIN), which are

internally terminated with 50 Ω to an on-chip voltage reference

(VREF = 2.5 V typically). The minimum differential input level

required to achieve a BER of 1010 is 200 mV p-p.

LOCK DETECTOR OPERATION

The lock detector on the ADN2805 has three modes of

operation: normal mode, REFCLK mode, and static LOL mode.

Normal Mode

In normal mode, the ADN2805 locks onto 1.25 Gbps NRZ data

without the use of a reference clock as an acquisition aid. In this

mode, the lock detector monitors the frequency difference

between the VCO and the input data frequency, and deasserts

the loss-of-lock signal, which appears on Pin 16 (LOL) when

the VCO is within 250 ppm of the data frequency. This enables

the DLL/PLL, which pulls the VCO frequency in the remaining

amount and acquires phase lock. When locked, if the input

frequency error exceeds 1000 ppm (0.1%), the loss-of-lock

signal reasserts and control returns to the frequency loop,

which begins a new frequency acquisition. The LOL pin

remains asserted until the VCO locks onto a valid input data

stream to within 250 ppm frequency error. This hysteresis is

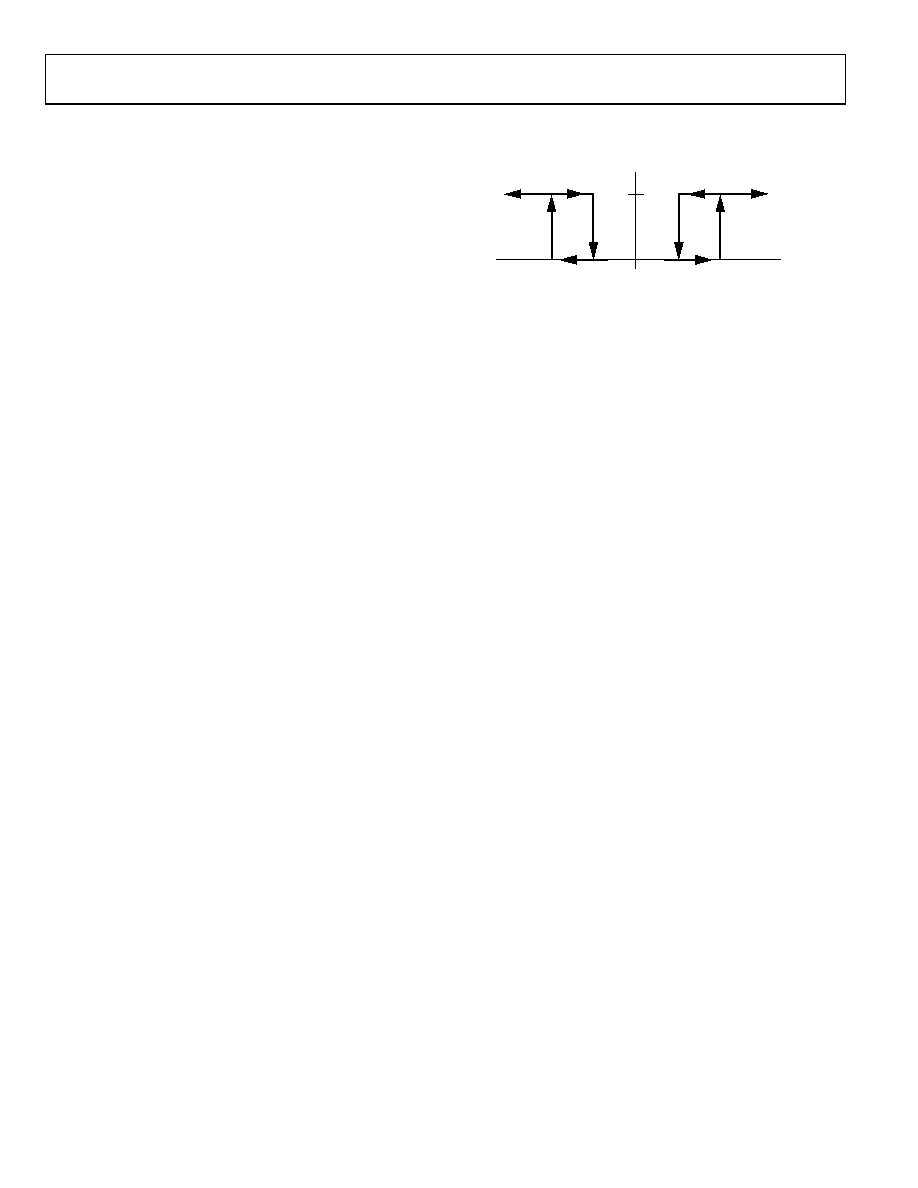

shown in Figure 13.

LOL

0

–250

250

1000

fVCO ERROR

(ppm)

–1000

1

071

21-

01

3

Figure 13. Transfer Function of LOL

LOL Detector Operation Using a Reference Clock

In REFCLK mode, a reference clock is used as an acquisition aid

to lock the ADN2805 VCO. Lock-to-reference mode is enabled

by setting CTRLA[0] to 1. The user also needs to write to the

CTRLA[7:6] and CTRLA[5:2] bits to set the reference frequency

range and the divide ratio of the data rate with respect to the

reference frequency. In this mode, the lock detector monitors

the difference in frequency between the divided down VCO

and the divided down reference clock. The loss-of-lock signal,

which appears on Pin 16 (LOL), deasserts when the VCO is

within 250 ppm of the desired frequency. This enables the DLL/

PLL, which pulls the VCO frequency in the remaining amount

with respect to the input data and acquires phase lock. When

locked, if the input frequency error exceeds 1000 ppm (0.1%),

the loss-of-lock signal reasserts and control returns to the fre-

quency loop, which reacquires with respect to the reference

clock. The LOL pin remains asserted until the VCO frequency

is within 250 ppm of the desired frequency. This hysteresis is

shown in Figure 13.

Static LOL Mode

The ADN2805 implements a static LOL feature to indicate

whether a loss-of-lock condition has ever occurred and remains

asserted, even if the ADN2805 regains lock, until the static LOL

bit is manually reset. The I2C register bit, MISC[4], is the static

LOL bit. If there is ever an occurrence of a loss-of-lock condition,

this bit internally asserts to Logic high. The MISC[4] bit remains

high even after the ADN2805 has reacquired lock to a new data

rate. This bit can be reset by writing a 1 followed by 0 to I2C

Register Bit CTRLB[6]. When reset, the MISC[4] bit remains

deasserted until another loss-of-lock condition occurs.

Writing a 1 to I2C Register Bit CTRLB[7] causes the LOL pin,

Pin 16, to become a static LOL indicator. In this mode, the LOL

pin mirrors the contents of the MISC[4] bit and has the function-

ality described in the previous paragraph.

The CTRLB[7] bit defaults to 0. In this mode, the LOL pin

operates in the normal operating mode, that is, it asserts only

when the ADN2805 is in acquisition mode and deasserts when

the ADN2805 reacquires lock.

相关PDF资料 |

PDF描述 |

|---|---|

| V375C36M150B2 | CONVERTER MOD DC/DC 36V 150W |

| V375C28M150BL3 | CONVERTER MOD DC/DC 28V 150W |

| SM840004-11KA | IC CLK SYNTHESIZER LN 20-TSSOP |

| AD9553BCPZ | IC INTEGER-N CLCK GEN 32LFCSP |

| MS27467T25F2P | CONN PLUG 100POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2805ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2805ACPZ-RL7 | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2806 | 制造商:AD 制造商全称:Analog Devices 功能描述:622 Mbps Clock and Data Recovery IC |

| ADN2806ACPZ | 功能描述:IC CLK/DATA REC 622MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2806ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 622MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。