- 您现在的位置:买卖IC网 > PDF目录1899 > ADP5588ACPZ-R7 (Analog Devices Inc)IC KEYPAD SCANNER GPIO PORT EXP PDF资料下载

参数资料

| 型号: | ADP5588ACPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/28页 |

| 文件大小: | 0K |

| 描述: | IC KEYPAD SCANNER GPIO PORT EXP |

| 标准包装: | 1 |

| 应用: | 键盘和警报系统 |

| 接口: | I²C |

| 电源电压: | 1.8 V ~ 3 V |

| 封装/外壳: | 24-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 24-LFCSP-VQ(4x4) |

| 包装: | 标准包装 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 799 (CN2011-ZH PDF) |

| 其它名称: | ADP5588ACPZ-R7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

ADP5588

Rev. C | Page 17 of 28

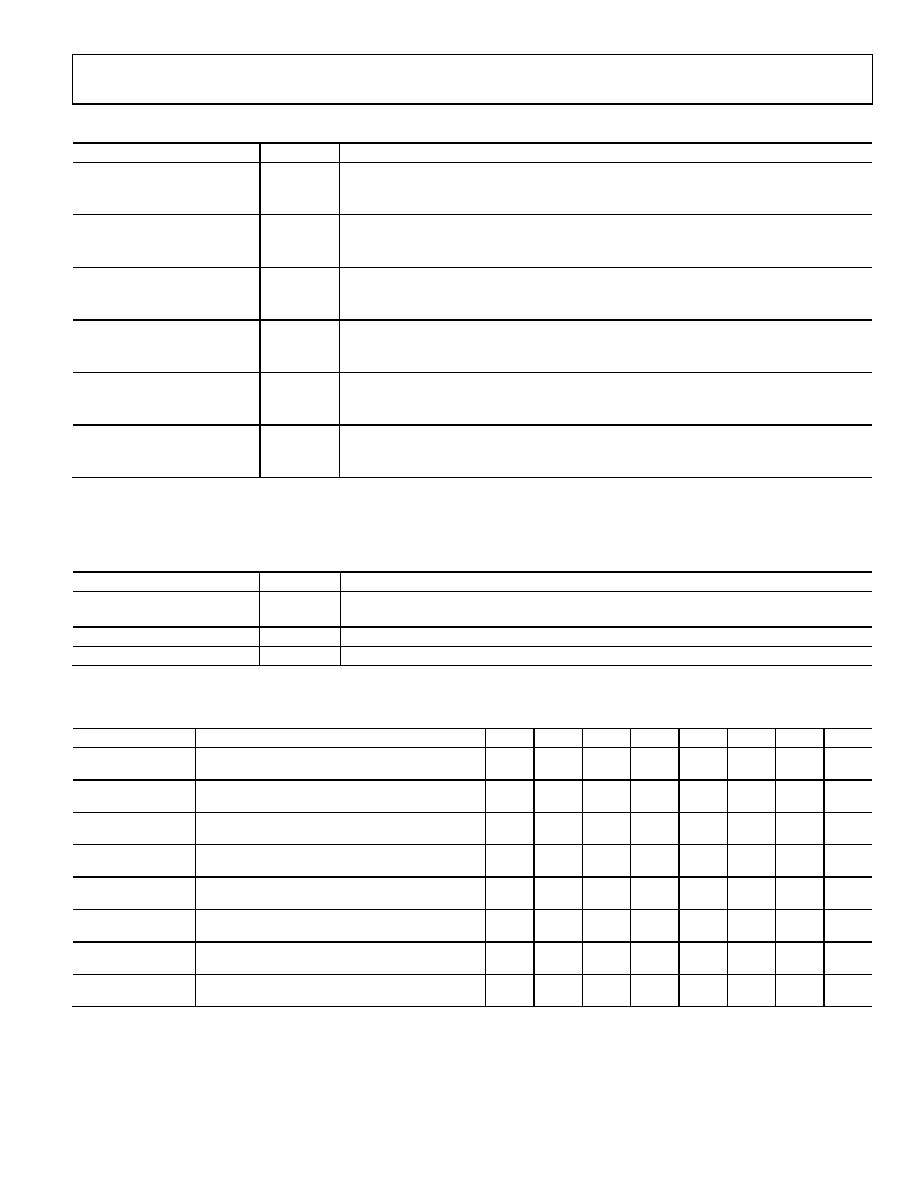

Table 20. INT_STAT—Register 0x02 (Interrupt Status Register)

Field

Bit

Description

CMP2_INT

5

Comparator interrupt status. When set, write 1 to clear.

1: Comparator 2 interrupt is detected.

0: Comparator 2 interrupt is not detected.

CMP1_INT

4

Comparator interrupt status. When set, write 1 to clear.

1: Comparator 1 interrupt is detected.

0: Comparator 1 interrupt is not detected.

OVR_FLOW_INT1

3

Overflow interrupt status. When set, write 1 to clear.

1: Overflow interrupt is detected.

0: Overflow interrupt is not detected.

K_LCK_INT2

2

Keylock interrupt status. When set, write 1 to clear.

1: Keylock interrupt is detected.

0: Keylock interrupt is not detected.

GPI_INT1, 3

1

GPI interrupt status. When set, write 1 to clear.

1: GPI interrupt is detected.

0: GPI interrupt is not detected.

KE_INT1, 3

0

Key events interrupt status. When set, write 1 to clear.

1: Key events interrupt is detected.

0: Key events interrupt is not detected.

1

The KE_INT, GPI_INT, and OVR_FLOW_INT bits reflect the status of the interrupts when the interrupt types are enabled even if the processor interrupt is masked.

2

The K_LCK_INT bit is the interrupt to the processor when the keypad lock sequence is triggered.

3

If there is a pending key event or GPI interrupt in their respective registers, KE_INT does not clear until the FIFO is empty, and the GPI_INT bit does not clear until the

cause of the interrupt is resolved. The host must write a 1 to the INT bits to clear.

Table 21. KEY_LCK_EC_STAT—Register 0x03 (Keylock and Event Counter Register)

Field

Bit

Description

K_LCK_EN

[6]

0: Lock feature is disabled.

1: Lock feature is enabled.

LCK2, LCK1

[5:4]

Keypad lock status[1:0] (00 = unlocked; 11 = locked; read only bits).

KEC1

[3:0]

Key event count of key event register.

1

The KEC bit indicates the key event count of key event registers that have values in the bit (KEC(0000) = 0 events, KEC(0001) = 1 event, KEC(1010) = 10 events. As the

key events are read and cleared, the state machine automatically reduces the event count on KEC.

Table 22. KEY_EVENTx—Register 0x04 to Register 0x0D (Key Event Register A to Key Event Register J)1

Register Name

Register Description

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

KEY_EVENTA

(Register 0x04)

Key Event Register A status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KA7

KA6

KA5

KA4

KA3

KA2

KA1

KA0

KEY_EVENTB

(Register 0x05)

Key Event Register B status (KE[6:0] = Key number),

KP[7 ]= 0: released, 1: pressed (cleared on read)

KB7

KB6

KB5

KB4

KB3

KB2

KB1

KB0

KEY_EVENTC

(Register 0x06)

Key Event Register C status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KC7

KC6

KC5

KC4

KC3

KC2

KC1

KC0

KEY_EVENTD

(Register 0x07)

Key Event Register B status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KD7

KD6

KD5

KD4

KD3

KD2

Kd1

KD0

KEY_EVENTE2

(Register 0x08)

Key Event Register B status (KE[6:0] = Key number),

KP[7]= 0: released, 1: pressed (cleared on read)

KE7

KE6

KE5

KE4

KE3

KE2

KE1

KE0

KEY_EVENTF

(Register 0x09)

Key Event Register B status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KF7

KF6

KF5

KF4

KF3

KF2

KF1

KF0

KEY_EVENTG

(Register 0x0A)

Key Event Register B status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KG7

KG6

KG5

KG4

KG3

KG2

KG1

KG0

KEY_EVENTH

(Register 0x0B)

Key Event Register B status (KE[6:0] = Key number),

KP[7] = 0: released, 1: pressed (cleared on read)

KH7

KH6

KH5

KH4

KH3

KH2

KH1

KH0

相关PDF资料 |

PDF描述 |

|---|---|

| ADP5589ACPZ-00-R7 | IC KEY DECODER 19I/O EXP 24LFCSP |

| ADSP-2104BPZ-80 | IC DSP CONTROLLER 16BIT 68PLCC |

| ADSP-21060LCW-160 | IC DSP CONTROLLER 32BIT 240CQFP |

| ADSP-21061KS-200 | IC DSP CONTROLLER 32BIT 240MQFP |

| ADSP-21065LCCA-240 | IC DSP CTLR 32BIT 196CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP5588ACPZ-R7B2 | 功能描述:Keypads and Alarm Systems Interface 24-LFCSP-WQ (4x4) 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:上次购买时间 应用:键盘和警报系统 接口:I2C 电压 - 电源:1.8 V ~ 3 V 封装/外壳:24-WFQFN 裸露焊盘,CSP 供应商器件封装:24-LFCSP-WQ(4x4) 安装类型:表面贴装 标准包装:1 |

| ADP5588-EVALZ | 功能描述:BOARD EVAL ADP5588 KEYPAD/GPIO RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| ADP5588XCPZ-R7 | 功能描述:Keypads and Alarm Systems Interface 制造商:analog devices inc. 系列:- 包装:- 零件状态:上次购买时间 应用:键盘和警报系统 接口:I2C 电压 - 电源:1.8 V ~ 3 V 封装/外壳:- 供应商器件封装:- 安装类型:- 标准包装:1 |

| ADP5588XCPZ-X2-R7 | 功能描述:Keypads and Alarm Systems Interface 制造商:analog devices inc. 系列:- 包装:- 零件状态:上次购买时间 应用:键盘和警报系统 接口:I2C 电压 - 电源:1.8 V ~ 3 V 封装/外壳:- 供应商器件封装:- 安装类型:- 标准包装:1 |

| ADP5589ACBZ-00-R7 | 功能描述:IC PORT EXPANDER 19I/O 25WLSCP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:* 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

发布紧急采购,3分钟左右您将得到回复。