- 您现在的位置:买卖IC网 > PDF目录1899 > ADSP-21061KS-200 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 240MQFP PDF资料下载

参数资料

| 型号: | ADSP-21061KS-200 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 52/52页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 240MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 同步串行端口(SSP) |

| 时钟速率: | 50MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 5.00V |

| 电压 - 核心: | 5.00V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BFQFP 裸露焊盘 |

| 供应商设备封装: | 240-MQFP-EP(32x32) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页

Rev. D | Page 9 of 52 | May 2013

PIN FUNCTION DESCRIPTIONS

ADSP-21061 pin definitions are listed below. All pins are identi-

cal on the ADSP-21061 and ADSP-21061L. Inputs identified as

synchronous (S) must meet timing requirements with respect to

CLKIN (or with respect to TCK for TMS, TDI). Inputs identi-

fied as asynchronous (A) can be asserted asynchronously to

CLKIN (or to TCK for TRST).

Unused inputs should be tied or pulled to VDD or GND, except

for ADDR31-0, DATA47-0, FLAG3-0, SW, and inputs that have

internal pull-up or pull-down resistors (CPA, ACK, DTx, DRx,

TCLKx, RCLKx, TMS, and TDI)—these pins can be left float-

ing. These pins have a logic-level hold circuit that prevents the

input from floating internally.

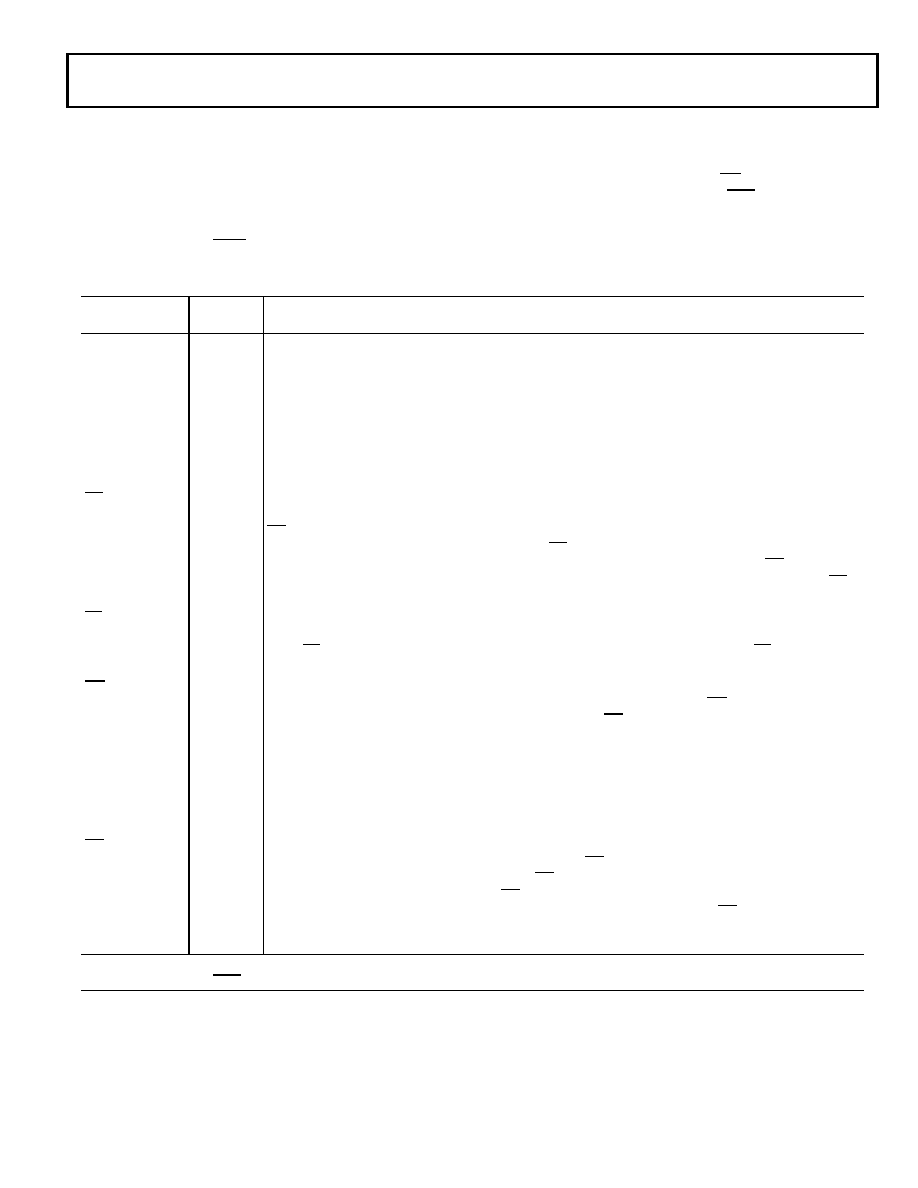

Table 2. Pin Descriptions

Pin

Type

Function

ADDR31–0

I/O/T

External Bus Address.

The ADSP-21061 outputs addresses for external memory and peripherals on these

pins. In a multiprocessor system the bus master outputs addresses for read/write of the internal memory or

IOP registers of other ADSP-21061s. The ADSP-21061 inputs addresses when a host processor or multipro-

cessing bus master is reading or writing its internal memory or IOP registers.

DATA47–0

I/O/T

External Bus Data.

The ADSP-21061 inputs and outputs data and instructions on these pins. 32-bit single-

precision floating-point data and 32-bit fixed-point data is transferred over Bits 47 to 16 of the bus. 40-bit

extended-precision floating-point data is transferred over Bits 47 to 8 of the bus. 16-bit short word data is

transferred over Bits 31 to 16 of the bus. In PROM boot mode, 8-bit data is transferred over Bits 23 to 16. Pull-

up resistors on unused DATA pins are not necessary.

MS3–0

O/T

Memory Select Lines.

These lines are asserted (low) as chip selects for the corresponding banks of external

memory. Memory bank size must be defined in the ADSP-21061’s system control register (SYSCON). The

MS3–0 lines are decoded memory address lines that change at the same time as the other address lines.

When no external memory access is occurring the MS3–0 lines are inactive; they are active however when a

conditional memory access instruction is executed, whether or not the condition is true. MS0 can be used

with the PAGE signal to implement a bank of DRAM memory (Bank 0). In a multiprocessing system the MS3–0

lines are output by the bus master.

RD

I/O/T

Memory Read Strobe.

This pin is asserted (low) when the ADSP-21061 reads from external memory devices

or from the internal memory of other ADSP-21061s. External devices (including other ADSP-21061s) must

assert RD to read from the ADSP-21061’s internal memory. In a multiprocessing system RD is output by the

bus master and is input by all other ADSP-21061s.

WR

I/O/T

Memory Write Strobe.

This pin is asserted (low) when the ADSP-21061 writes to external memory devices

or to the internal memory of other ADSP-21061s. External devices must assert WR to write to the

ADSP-21061’s internal memory. In a multiprocessing system WR is output by the bus master and is input by

all other ADSP-21061s.

PAGE

O/T

DRAM Page Boundary.

The ADSP-21061 asserts this pin to signal that an external DRAM page boundary

has been crossed. DRAM page size must be defined in the ADSP-21061’s memory control register (WAIT).

DRAM can only be implemented in external memory Bank 0; the PAGE signal can only be activated for

Bank 0 accesses. In a multiprocessing system PAGE is output by the bus master.

ADRCLK

O/T

Clock Output Reference.

In a multiprocessing system ADRCLK is output by the bus master.

SW

I/O/T

Synchronous Write Select.

This signal is used to interface theADSP-21061to synchronousmemorydevices

(including other ADSP-21061s). The ADSP-21061 asserts SW (low) to provide an early indication of an

impending write cycle, which can be aborted if WR is not later asserted (e.g., in a conditional write

instruction). In a multiprocessing system, SW is output by the bus master and is input by all other

ADSP-21061s to determine if the multiprocessor memory access is a read or write. SWis asserted at the same

time as the address output. A host processor using synchronous writes must assert this pin when writing to

the ADSP-21061(s).

A = Asynchronous, G = Ground, I = Input, O = Output, P = Power Supply, S = Synchronous, (A/D) = Active Drive, (O/D) = Open-Drain,

T = Three-State (when SBTS is asserted, or when the ADSP-21061 is a bus slave)

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21065LCCA-240 | IC DSP CTLR 32BIT 196CSPBGA |

| ADSP-2111BG-80 | IC DSP CONTROLLER 16BIT 100PGA |

| ADSP-21160MKB-80 | IC DSP CONTROLLER 32BIT 400 BGA |

| ADSP-21160NCB-100 | IC DSP CONTROLLER 32BIT 400BGA |

| ADSP-21161NCCA-100 | IC DSP CONTROLLER 32BIT 225MBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21061KS-200X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:32-Bit Digital Signal Processor |

| ADSP-21061KSZ-133 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21061KSZ-160 | 功能描述:IC DSP CONTROLLER 1MBIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061KSZ-200 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061L | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。