- 您现在的位置:买卖IC网 > PDF目录19376 > ADSP-21061LKB-160 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 225BGA PDF资料下载

参数资料

| 型号: | ADSP-21061LKB-160 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/52页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 225BGA |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 同步串行端口(SSP) |

| 时钟速率: | 40MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 3.30V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 225-BBGA |

| 供应商设备封装: | 225-PBGA |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Rev. D | Page 26 of 52 | May 2013

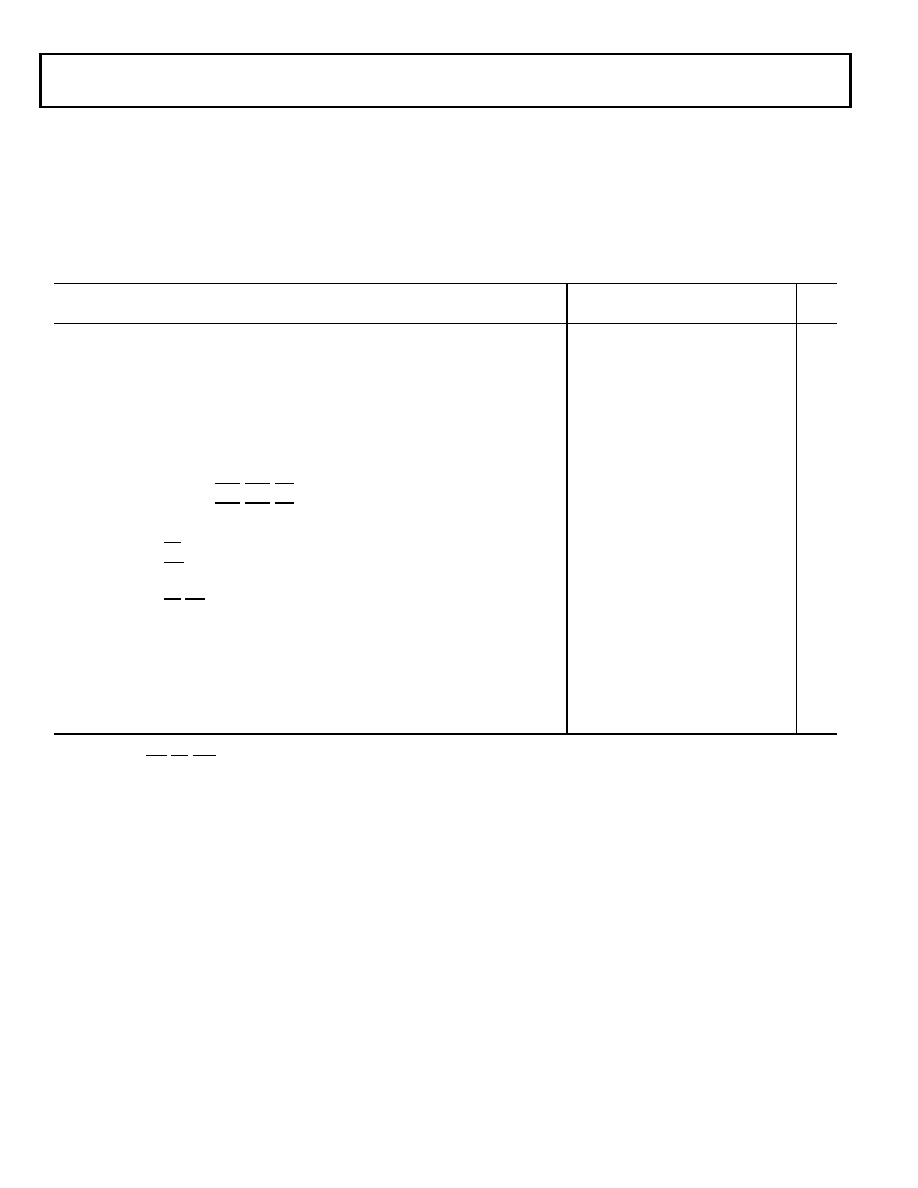

Synchronous Read/Write—Bus Master

Use these specifications for interfacing to external memory sys-

tems that require CLKIN—relative timing or for accessing a

slave ADSP-21061 (in multiprocessor memory space). These

synchronous switching characteristics are also valid during

asynchronous memory reads and writes except where noted (see

Bus Master on Page 25). When accessing a slave ADSP-21061,

these switching characteristics must meet the slave’s timing

requirements for synchronous read/writes (see Synchronous

Read/Write—Bus Slave on Page 28). The slave ADSP-21061

must also meet these (bus master) timing requirements for data

and acknowledge setup and hold times.

Table 14. Synchronous Read/Write—Bus Master

5 V and 3.3 V

Unit

Parameter

Min

Max

Timing Requirements

tSSDATI

Data Setup Before CLKIN

(50 MHz, tCK = 20 ns)1

2 + DT/8

1.5 + DT/8

ns

tHSDATI

Data Hold After CLKIN

3.5 – DT/8

ns

tDAAK

ACK Delay After Address, Selects2, 3

15 + 7DT/8 + W

ns

tSACKC

ACK Setup Before CLKIN3

6.5+DT/4

ns

tHACK

ACK Hold After CLKIN

–1 – DT/4

ns

Switching Characteristics

tDADRO

Address, MSx, BMS, SW Delay After CLKIN2

6.5 – DT/8

ns

tHADRO

Address, MSx, BMS, SW Hold After CLKIN

–1 – DT/8

ns

tDPGC

PAGE Delay After CLKIN

9 + DT/8

16 + DT/8

ns

tDRDO

RD High Delay After CLKIN

–1.5 – DT/8

4 – DT/8

ns

tDWRO

WR High Delay After CLKIN

(50 MHz, tCK = 20 ns)

–2.5 – 3DT/16

–1.5 – 3DT/16

4 – 3DT/16

ns

tDRWL

RD/WR Low Delay After CLKIN

8 + DT/4

12 + DT/4

ns

tSDDATO

Data Delay After CLKIN

19 + 5DT/16

ns

tDATTR

Data Disable After CLKIN4

0 – DT/8

7 – DT/8

ns

tDADCCK

ADRCLK Delay After CLKIN

4 + DT/8

10 + DT/8

ns

tADRCK

ADRCLK Period

tCK

ns

tADRCKH

ADRCLK Width High

(tCK/2 – 2)

ns

tADRCKL

ADRCLK Width Low

(tCK/2 – 2)

ns

1 This specification applies to the ADSP-21061KS-200 (5 V, 50 MHz) operating at t

CK < 25 ns. For all other devices, use the preceding timing specification of the same name.

2 The falling edge of MSx, SW, BMS is referenced.

3 ACK delay/setup: User must meet tDAAK or tDSAK or synchronous specification tSAKC for deassertion of ACK (low), all three specifications must be met for assertion of ACK

(high).

4 See Example System Hold Time Calculation on Page 43 for calculation of hold times given capacitive and dc loads.

相关PDF资料 |

PDF描述 |

|---|---|

| GBM10DTKT-S288 | CONN EDGECARD 20POS .156 EXTEND |

| HWS300-5 | PWR SUP IND 5V 60A SNG OUTPUT |

| VI-B2Y-CX-F4 | CONVERTER MOD DC/DC 3.3V 49.5W |

| VI-B2Y-CX-F1 | CONVERTER MOD DC/DC 3.3V 49.5W |

| TAJY107M016RNJ | CAP TANT 100UF 16V 20% 2917 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21061LKB-176 | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer Family |

| ADSP-21061LKBZ-160 | 功能描述:IC DSP CONTROLLER 32BIT 225-BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP21061LKS160 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 40MHz 40MIPS 240-Pin MQFP Tray |

| ADSP-21061LKS-160 | 制造商:Rochester Electronics LLC 功能描述:ADSP-21061 1MBIT,40MHZ, 3V SHARC - Bulk 制造商:Analog Devices 功能描述:IC SHARC DSP 40MHZ 21061 MQFP240 |

| ADSP-21061LKS-176 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 44MHz 44MIPS 240-Pin MQFP Tray 制造商:Rochester Electronics LLC 功能描述:ADSP-21061L 44HZ, 3V SHARC - Bulk |

发布紧急采购,3分钟左右您将得到回复。