- 您现在的位置:买卖IC网 > PDF目录19396 > ADSP-BF524KBCZ-3C2 (Analog Devices Inc)IC DSP CTRLR 300MHZ 289CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF524KBCZ-3C2 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/36页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTRLR 300MHZ 289CSPBGA |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | DMA,I²C,PPI,SPI,SPORT,UART,USB |

| 时钟速率: | 300MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.30V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 289-LFBGA,CSPBGA |

| 供应商设备封装: | 289-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页

Rev. A

|

Page 6 of 36

|

March 2010

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

The programmer can simultaneously load the volume control of

both channels by writing to the LRHPBOTH (Register R2, Bit

D8) and RLHPBOTH (Register R3, Bit D8) bits of the left- or

right-channel DAC volume registers.

The maximum output level of the headphone outputs is

1.0 V rms when AVDD and HPVDD = 3.3 V. To suppress audi-

ble pops and clicks, the headphone and line outputs are held at

the VMID dc voltage level when the device is set to standby

mode or when the headphone outputs are muted.

The stereo line outputs of the codec, the LOUT and ROUT pins,

can drive a load impedance of 10 k

Ω and 50 pF. The line output

signal levels are not adjustable at the output mixer, which has a

fixed gain of 0 dB. The maximum output level of the line out-

puts is 1.0 V rms when AVDD = 3.3 V.

DIGITAL AUDIO INTERFACE

The digital audio input can support the following digital audio

communication protocols: right-justified mode, left-justified

through Figure 10 on Page 7.

The mode selection is performed by writing to the FORMAT

bits of the digital audio interface register (Register R7, Bit D1

and Bit D0). All modes are MSB first and operate with data of 16

to 32 bits.

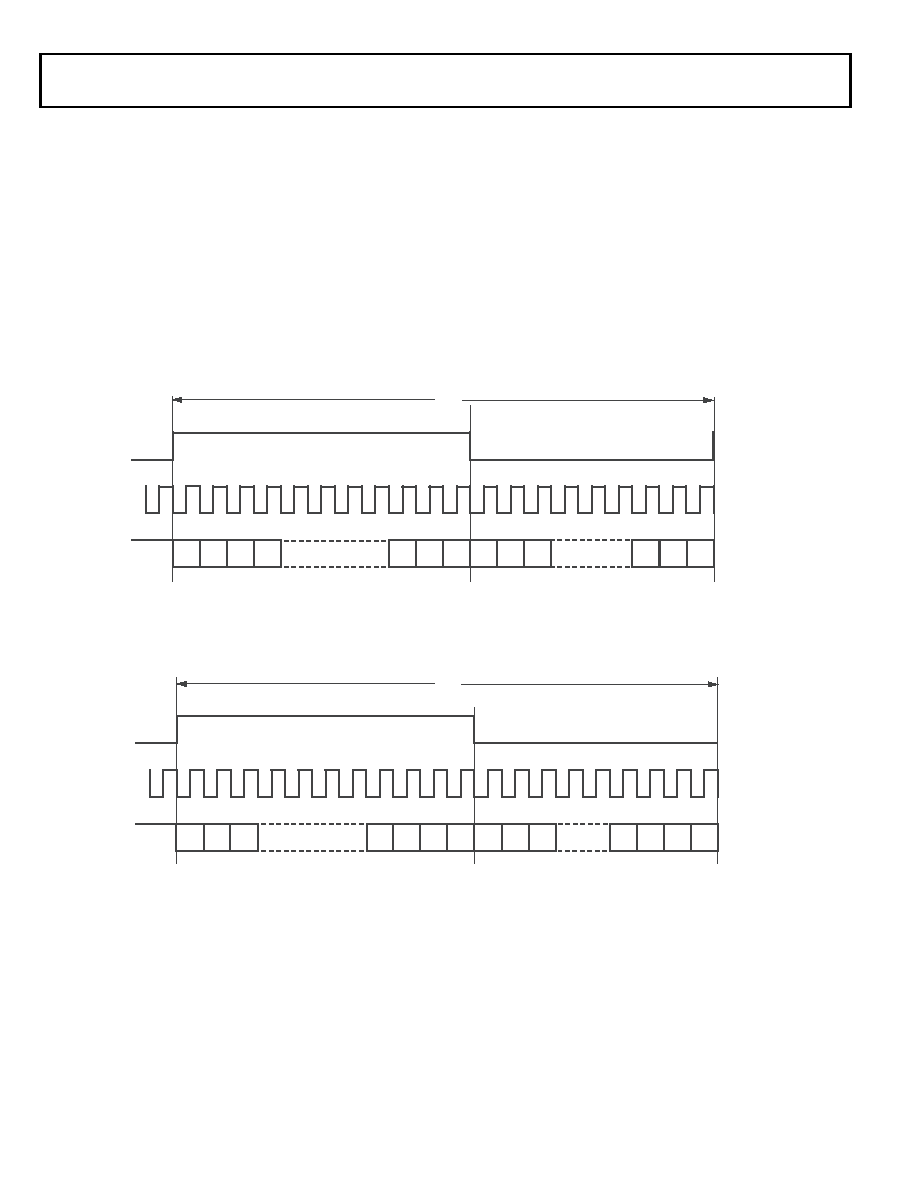

Figure 6. Left-Justified Audio Input Mode

Figure 7. Right-Justified Audio Input Mode

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

1234

N

X

N

12

LEFT CHANNEL

3

RIGHT CHANNEL

1/

fS

X = DON’T CARE.

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

LEFT CHANNEL

RIGHT CHANNEL

1/

fS

X = DON’T CARE.

XN

X

3

2

1

XXN

4

4321

相关PDF资料 |

PDF描述 |

|---|---|

| HMC35DRTS-S93 | CONN EDGECARD 70POS DIP .100 SLD |

| TAJC474K050RNJ | CAP TANT 0.47UF 50V 10% 2312 |

| HMC35DRES-S93 | CONN EDGECARD 70POS .100 EYELET |

| TAJC227M006RNJ | CAP TANT 220UF 6.3V 20% 2312 |

| MAX6519UKP110+T | IC TEMP SENSOR SW SOT23-5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF524KBCZ-4 | 功能描述:IC DSP CTRLR 400MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF524KBCZ-4AX | 制造商:Analog Devices 功能描述: |

| ADSP-BF524KBCZ-4C2 | 功能描述:IC DSP CTRLR 400MHZ 289CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF525 | 制造商:Analog Devices 功能描述: |

| ADSP-BF525ABCZ-5 | 功能描述:数字信号处理器和控制器 - DSP, DSC ADSP-BF525 Processor 533Mhz Ethernet USB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。