- 您现在的位置:买卖IC网 > PDF目录19467 > ADSP-BF527KBCZ-6C2 (Analog Devices Inc)IC DSP 16BIT 600MHZ 289CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF527KBCZ-6C2 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/88页 |

| 文件大小: | 0K |

| 描述: | IC DSP 16BIT 600MHZ 289CSPBGA |

| 产品变化通告: | Datasheet Specification Change 14/Dec/2009 |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | DMA,以太网,I²C,PPI,SPI,SPORT,UART,USB |

| 时钟速率: | 600MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.10V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 289-LFBGA,CSPBGA |

| 供应商设备封装: | 289-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | EVAL-SDP-CB1Z-ND - BOARD EVALUATION FOR SDP-CB1 ADZS-BF527-MPSKIT-ND - BOARD EVAL MEDIA PLAYER BF527 ADZS-BF527-EZLITE-ND - BOARD EVAL ADSP-BF527 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

�� �

�

�

�ADSP-BF522/ADSP-BF523/ADSP-BF524/ADSP-BF525/ADSP-BF526/ADSP-BF527�

��register.� Set� this� register� prior� to� using� the� TWI� port.�

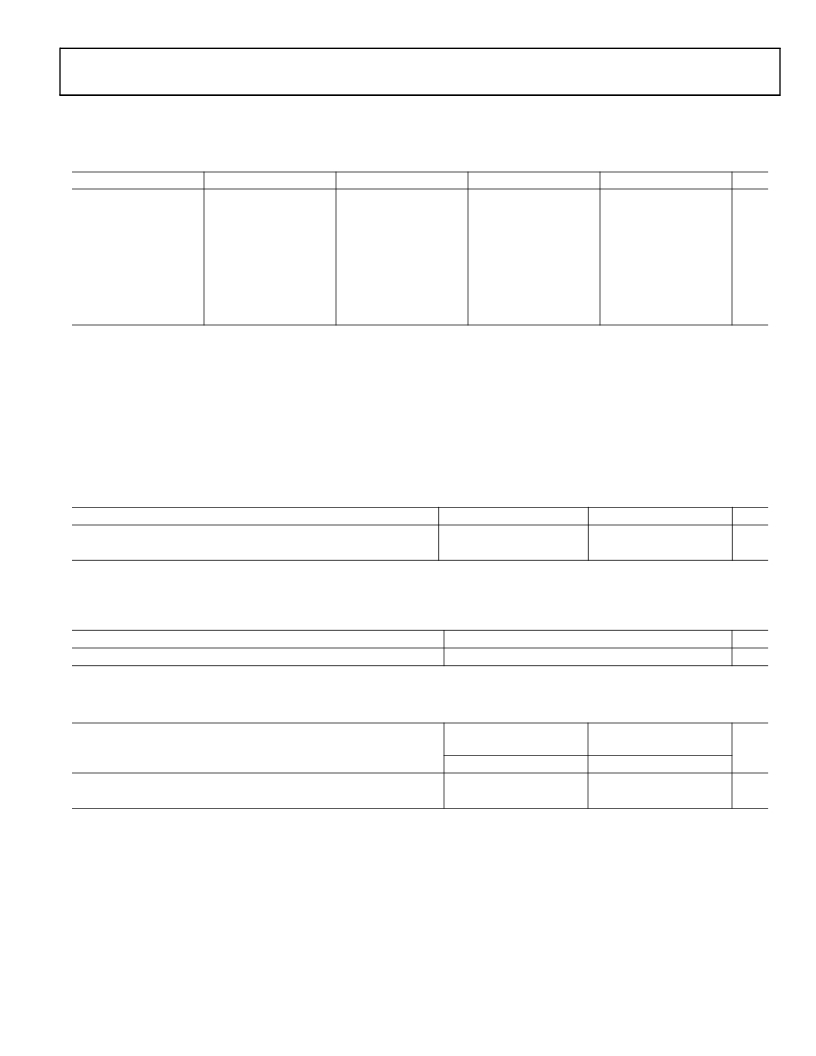

�Table� 11.� TWI_DT� Field� Selections� and� V� DDEXT� /V� BUSTWI�

�TWI_DT�

�000� (default)� 1�

�001�

�010�

�011�

�100�

�101�

�110�

�111� (reserved)�

�V� DDEXT� Nominal�

�3.3�

�1.8�

�2.5�

�1.8�

�3.3�

�1.8�

�2.5�

�–�

�V� BUSTWI� Min�

�2.97�

�1.7�

�2.97�

�2.97�

�4.5�

�2.25�

�2.25�

�–�

�V� BUSTWI� Nominal�

�3.3�

�1.8�

�3.3�

�3.3�

�5�

�2.5�

�2.5�

�–�

�V� BUSTWI� Max�

�3.63�

�1.98�

�3.63�

�3.63�

�5.5�

�2.75�

�2.75�

�–�

�Unit�

�V�

�V�

�V�

�V�

�V�

�V�

�V�

�–�

�1�

�Designs� must� comply� with� the� V� DDEXT� and� V� BUSTWI� voltages� specified� for� the� default� TWI_DT� setting� for� correct� JTAG� boundary� scan� operation� during� reset.�

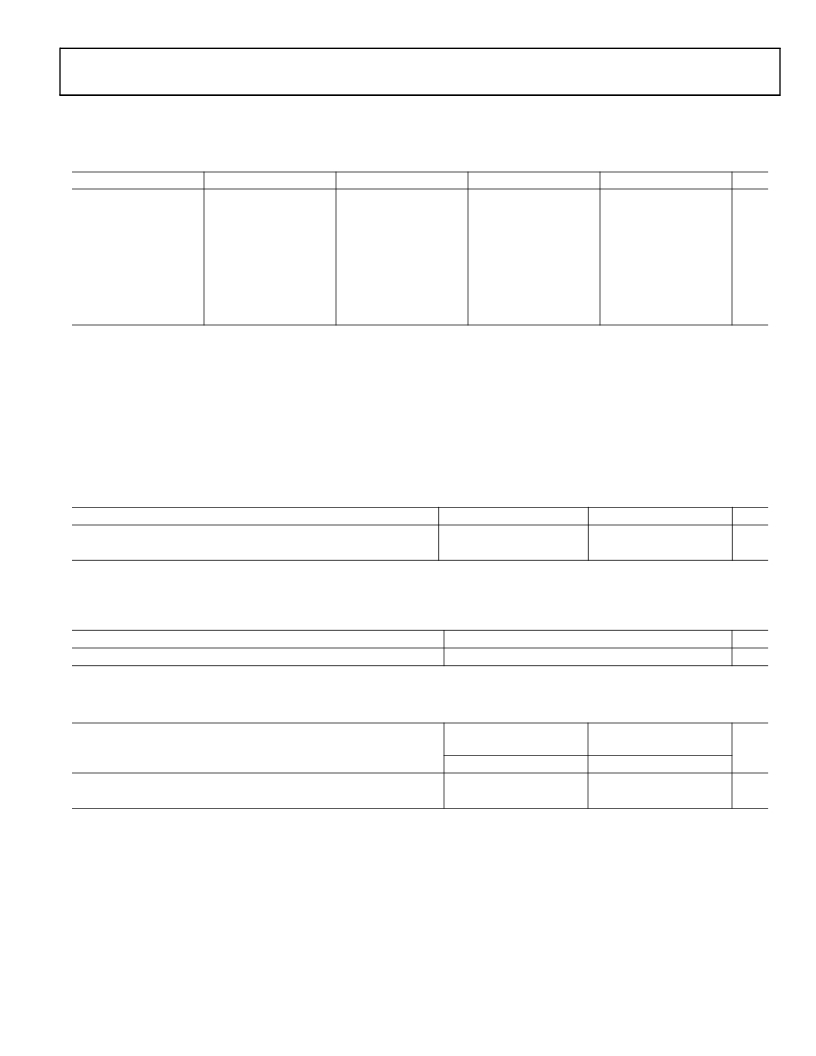

�Clock� Related� Operating� Conditions�

�for� ADSP-BF522/ADSP-BF524/ADSP-BF526� Processors�

��ADSP-BF522/ADSP-BF524/ADSP-BF526� processors.� Take� care�

�in� selecting� MSEL,� SSEL,� and� CSEL� ratios� so� as� not� to� exceed� the�

��describes� phase-locked� loop� operating� conditions.�

�Table� 12.� Core� Clock� (CCLK)� Requirements� (All� Instruction� Rates� 1� )� for� ADSP-BF522/ADSP-BF524/ADSP-BF526� Processors�

�Parameter�

�Nominal� Voltage� Setting�

�Max�

�Unit�

�f� CCLK�

�f� CCLK�

�Core� Clock� Frequency� (V� DDINT� =1.33� V� minimum)�

�Core� Clock� Frequency� (V� DDINT� =� 1.235� V� minimum)�

�1.40� V�

�1.30� V�

�400� 2�

�300�

�MHz�

�MHz�

�1�

�2�

���Table� 13.� Phase-Locked� Loop� Operating� Conditions� for� ADSP-BF522/ADSP-BF524/ADSP-BF526� Processors�

�Parameter�

�Min�

�Max�

�Unit�

�f� VCO�

�Voltage� Controlled� Oscillator� (VCO)� Frequency�

�70�

�Instruction� Rate� 1�

�MHz�

�1�

��Table� 14.� SCLK� Conditions� for� ADSP-BF522/ADSP-BF524/ADSP-BF526� Processors�

�V� DDEXT� /V� DDMEM�

�1.8� V� Nominal� 1�

�V� DDEXT� /V� DDMEM�

�2.5� V� or� 3.3� V� Nominal�

�Parameter�

�Max�

�Max�

�Unit�

�f� SCLK�

�f� SCLK�

�CLKOUT/SCLK� Frequency� (V� DDINT� ≥� 1.33� V)� 2�

�CLKOUT/SCLK� Frequency� (V� DDINT� <� 1.33� V)�

�80�

�80�

�100�

�80�

�MHz�

�MHz�

�1�

�2�

�If� either� V� DDEXT� or� V� DDMEM� are� operating� at� 1.8� V� nominal,� f� SCLK� is� constrained� to� 80� MHz.�

�f� SCLK� must� be� less� than� or� equal� to� f� CCLK� and� is� subject� to� additional� restrictions� for� SDRAM� interface� operation.� See� Table� 37� on� Page� 47� .�

�Rev.� D� |�

�Page� 29� of� 88� |� July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6695AUB+ | IC SENSOR TEMP SMBUS 10-UMAX |

| XCR3256XL-7PQ208C | IC CPLD 256MCELL 3.3V HP 208PQFP |

| GCC05DREN | CONN EDGECARD 10POS .100 EYELET |

| VE-21J-CY-F4 | CONVERTER MOD DC/DC 36V 50W |

| VE-B12-CX-B1 | CONVERTER MOD DC/DC 15V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF527KBCZ6C2X | 制造商:Analog Devices 功能描述: |

| ADSP-BF527KBCZ-6X | 制造商:Analog Devices 功能描述:DSP 32-Bit 600MHz 208-Pin CSP-BGA 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF527KBCZ-ENG | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF527KBCZENGA | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:LOW POWER BLACKFIN PROCESSOR WITH ADVANCED PERIPHERALS - Trays |

| ADSPBF527KBCZENGC1 | 制造商:Analog Devices 功能描述:- Trays |

发布紧急采购,3分钟左右您将得到回复。