- 您现在的位置:买卖IC网 > PDF目录19462 > ADSP-TS201SABPZ060 (Analog Devices Inc)IC PROCESSOR 600MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS201SABPZ060 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/48页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR 600MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 3MB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 配用: | ADZS-TS201S-EZLITE-ND - KIT LITE EVAL FOR ADSP-TS201S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-TS201S

Rev. C

|

Page 31 of 48

|

December 2006

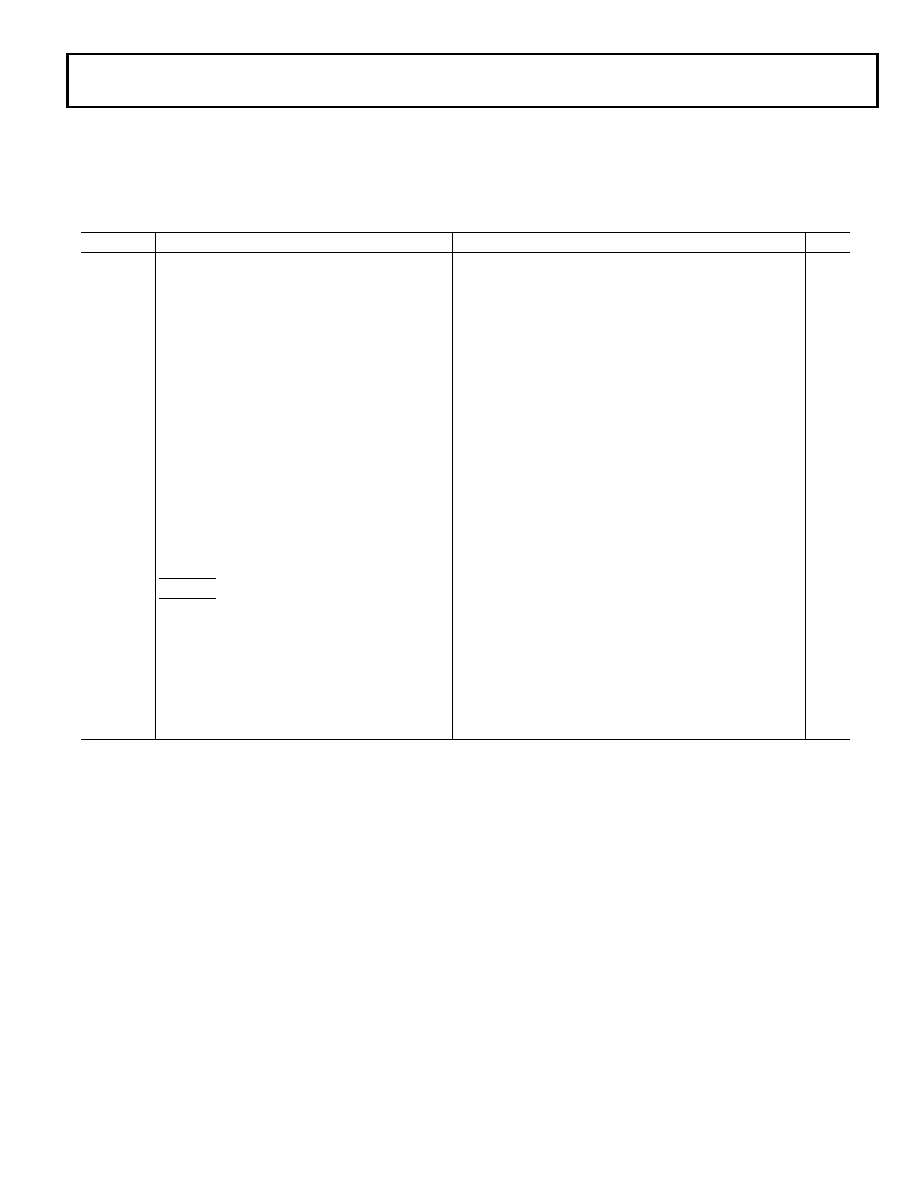

Link Port—Data Out Timing

Figure 22, and Figure 23 provide the data out timing for the

LVDS link ports.

Table 32. Link Port—Data Out Timing

Parameter Description

Min

Max

Unit

Outputs

tREO

Rising Edge (Figure 19)350

ps

tFEO

Falling Edge (Figure 19)350

ps

tLCLKOP

LxCLKOUT Period (Figure 18)

Greater of 2.0 or

0.9

× LCR × tCCLK1, 2, 3

Smaller of 12.5 or

1.1

× LCR × tCCLK1, 2, 3 ns

tLCLKOH

LxCLKOUT High (Figure 18)0.4

× tLCLKOP1

0.6

× tLCLKOP1

ns

tLCLKOL

LxCLKOUT Low (Figure 18)0.4

× tLCLKOP1

0.6

× tLCLKOP1

ns

tCOJT

LxCLKOUT Jitter (Figure 18)

±1504, 5, 6

±2507

ps

tLDOS

LxDATO Output Setup (Figure 20)0.25

× LCR × tCCLK –0.10 × tCCLK1, 4, 8

0.25

× LCR × tCCLK –0.15 × tCCLK1, 5, 6, 8

0.25

× LCR × tCCLK –0.30 × tCCLK 1, 7, 8

ns

tLDOH

LxDATO Output Hold (Figure 20)0.25

× LCR × tCCLK –0.10 × tCCLK1, 4, 8

0.25

× LCR × tCCLK –0.15 × tCCLK1, 5, 6, 8

0.25

× LCR × tCCLK –0.30 × tCCLK 1, 7, 8

ns

tLACKID

Delay from LxACKI rising edge to first transmission

clock edge (Figure 21)

16

× LCR × tCCLK1, 2

ns

tBCMPOV

LxBCMPO Valid (Figure 21)2

× LCR × tCCLK1, 2

ns

tBCMPOH

LxBCMPO Hold (Figure 22)3

× TSW – 0.51, 9

ns

Inputs

tLACKIS

LxACKI low setup to guarantee that the transmitter

stops transmitting (Figure 22)

LxACKI high setup to guarantee that the transmitter

continues its transmission without any interruption

(Figure 23)16

× LCR × tCCLK1, 2

ns

tLACKIH

LxACKI High Hold Time (Figure 23)0.51

ns

1 Timing is relative to the 0 differential voltage (VOD = 0).

2 LCR (link port clock ratio) = 1, 1.5, 2, or 4. t

CCLK is the core period.

3 For the cases of tLCLKOP = 2.0 ns and tLCLKOP = 12.5 ns, the effect of tCOJT specification on output period must be considered.

4 LCR= 1.

5 LCR= 1.5.

6 LCR= 2.

7 LCR= 4.

8 The t

LDOS and tLDOH values include LCLKOUT jitter.

9 TSW is a short-word transmission period. For a 4-bit link, it is 2

× LCR × tCCLK. For a 1-bit link, it is 8 × LCR × tCCLK ns.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2WX-CY-F1 | CONVERTER MOD DC/DC 5.2V 50W |

| TPSC156K020H0450 | CAP TANT 15UF 20V 10% 2312 |

| 182-025-213R161 | CONN DB25 FEMAL .318" R/A NICKEL |

| EEM10DSEF | CONN EDGECARD 20POS .156 EYELET |

| VE-2WW-CY-F1 | CONVERTER MOD DC/DC 5.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS201SBBPZ050 | 功能描述:IC PROCESSOR 500MHZ 575BGA 制造商:analog devices inc. 系列:TigerSHARC? 包装:托盘 零件状态:上次购买时间 类型:定点/浮点 接口:主机接口,连接端口,多处理器 时钟速率:500MHz 非易失性存储器:外部 片载 RAM:3MB 电压 - I/O:2.50V 电压 - 内核:1.05V 工作温度:-40°C ~ 85°C(TC) 安装类型:表面贴装 封装/外壳:576-BBGA 裸露焊盘 供应商器件封装:576-BGA-ED(25x25) 标准包装:1 |

| ADSP-TS201SWBP-050 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 500MHz 500MIPS 576-Pin BGA |

| ADSP-TS201SYBP-050 | 功能描述:IC PROCESSOR 500MHZ 576-SBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS201SYBPZ050 | 功能描述:IC PROCESSOR 500MHZ 576-SBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-TS202SABP-050 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 500MHz 500MIPS 576-Pin TEBGA 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT 500MHZ 500MIPS 576PIN TEBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。