- 您现在的位置:买卖IC网 > PDF目录10950 > ADV212BBCZRL-115 (Analog Devices Inc)IC CODEC VID JPEG 2000 121CSPBGA PDF资料下载

参数资料

| 型号: | ADV212BBCZRL-115 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/44页 |

| 文件大小: | 0K |

| 描述: | IC CODEC VID JPEG 2000 121CSPBGA |

| 标准包装: | 1 |

| 系列: | Wavescale® |

| 类型: | JPEG2000 视频编解码器 |

| 分辨率(位): | 16 b |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 1.5V,3.3V |

| 电压 - 电源,数字: | 1.5V,3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 121-BGA,CSPBGA |

| 供应商设备封装: | 121-CSPBGA(12x12) |

| 包装: | 标准包装 |

| 产品目录页面: | 776 (CN2011-ZH PDF) |

| 配用: | ADV212-HD-EB-ND - BOARD EVALUATION FOR ADV212-HD |

| 其它名称: | ADV212BBCZRL-115DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

ADV212

Rev. B | Page 21 of 44

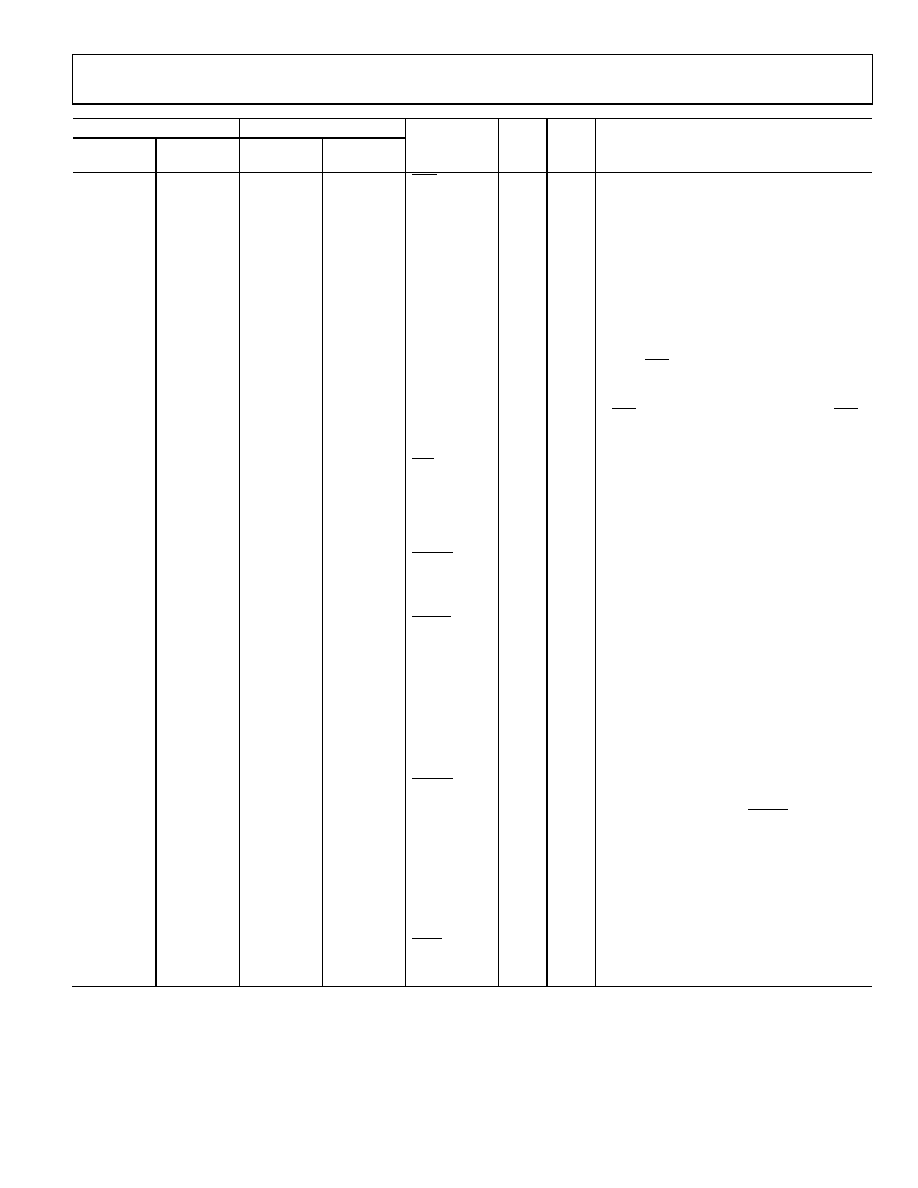

121-Ball Package

144-Ball Package

Pin No.

Location

Pin No.

Location

Mnemonic

Pins

Used

Type

Description

85

H8

83

G11

ACK

1

O

Acknowledge. Used for direct register accesses.

This signal indicates that the last register access

was successful. Due to synchronization issues,

control and status register accesses may incur an

additional delay; therefore, the host software

should wait for acknowledgment from the

ADV212 before attempting another register

access.

Accesses to the FIFOs (external DMA modes),

on the other hand, are guaranteed to occur

immediately, provided that space is available;

therefore, the host software does not need to

wait for ACK before attempting another register

access, provided that the timing constraints

are observed.

If ACK is shared with more than one device, ACK

should be connected to a pull-up resistor (10 k )

and the PLL_HI register, Bit 4, must be set to 1.

76

G10

82

G10

IRQ

1

O

Interrupt. This pin indicates that the ADV212

requires the attention of the host processor.

This pin can be programmed to indicate the

status of the internal interrupt conditions

within the ADV212. The interrupt sources are

enabled via the bits in the EIRQIE register.

63

F8

72

F12

DREQ0

1

O

Data Request for External DMA Interface.

Indicates that the ADV212 is ready to

send/receive data to/from the FIFO assigned

to DMA Channel 0.

FSRQ0

O

FIFO Service Request. Used in DCS-DMA

mode. Service request from the FIFO assigned

to Channel 0 (asynchronous mode).

VALID

O

Valid Indication for JDATA Input/Output Stream.

Polarity of this pin is programmable in the

EDMOD0 register. VALID is always an output.

CFG1

I

Boot Mode Configuration. This pin is read on

reset to determine the boot configuration of

the on-board processor. The pin should be

tied to IOVDD through a 10 k resistor.

64

F9

71

F11

DACK0

1

I

Data Acknowledge for External DMA Interface.

Signal from the host CPU, which indicates that

the data transfer request (DREQ0) has been

acknowledged and that the data transfer can

proceed. This pin must be held high at all

times if the DMA interface is not used, even if

the DMA channels are disabled.

HOLD

I

External Hold Indication for JDATA Input/Output

Stream. Polarity is programmable in the

EDMOD0 register. This pin is always an input.

FCS0

I

FIFO Chip Select. Used in DCS-DMA mode.

Chip select for the FIFO assigned to Channel 0

(asynchronous mode).

相关PDF资料 |

PDF描述 |

|---|---|

| MC9S12XA256VAA | IC MCU 256K FLASH 80-QFP |

| VI-B5N-IX-B1 | CONVERTER MOD DC/DC 18.5V 75W |

| VI-2N4-IY-F4 | CONVERTER MOD DC/DC 48V 50W |

| MCIMX351AVM4BR2 | IC MPU I.MX35 400MAPBGA |

| VI-B6V-IW-B1 | CONVERTER MOD DC/DC 5.8V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV212BBCZRL-150 | 功能描述:IC CODEC VID JPEG 2000 144CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:Wavescale® 标准包装:2,500 系列:- 类型:PCM 数据接口:PCM 音频接口 分辨率(位):15 b ADC / DAC 数量:1 / 1 三角积分调变:是 S/N 比,标准 ADC / DAC (db):- 动态范围,标准 ADC / DAC (db):- 电压 - 电源,模拟:2.7 V ~ 3.3 V 电压 - 电源,数字:2.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-VFBGA 供应商设备封装:80-BGA MICROSTAR JUNIOR(5x5) 包装:带卷 (TR) 其它名称:296-21257-2 |

| ADV212-HD-EB | 功能描述:BOARD EVALUATION FOR ADV212-HD RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ADV212XBCZ-150 | 制造商:Analog Devices 功能描述:JPEG2000 VIDEO CODEC - Bulk |

| ADV216BBCZ | 制造商:Analog Devices 功能描述:- Trays |

| ADV226KBCZ | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。