- 您现在的位置:买卖IC网 > PDF目录11354 > ADV3229ACPZ (Analog Devices Inc)IC CROSSPOINT SW 16X8 72LFCSP PDF资料下载

参数资料

| 型号: | ADV3229ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/24页 |

| 文件大小: | 0K |

| 描述: | IC CROSSPOINT SW 16X8 72LFCSP |

| 标准包装: | 1 |

| 功能: | 交叉点开关 |

| 电路: | 1 x 8:8 |

| 电压电源: | 双电源 |

| 电压 - 电源,单路/双路(±): | ±5V |

| 电流 - 电源: | 58mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 72-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 72-LFCSP-VQ(10x10) |

| 包装: | 托盘 |

ADV3228/ADV3229

Rev. 0 | Page 5 of 24

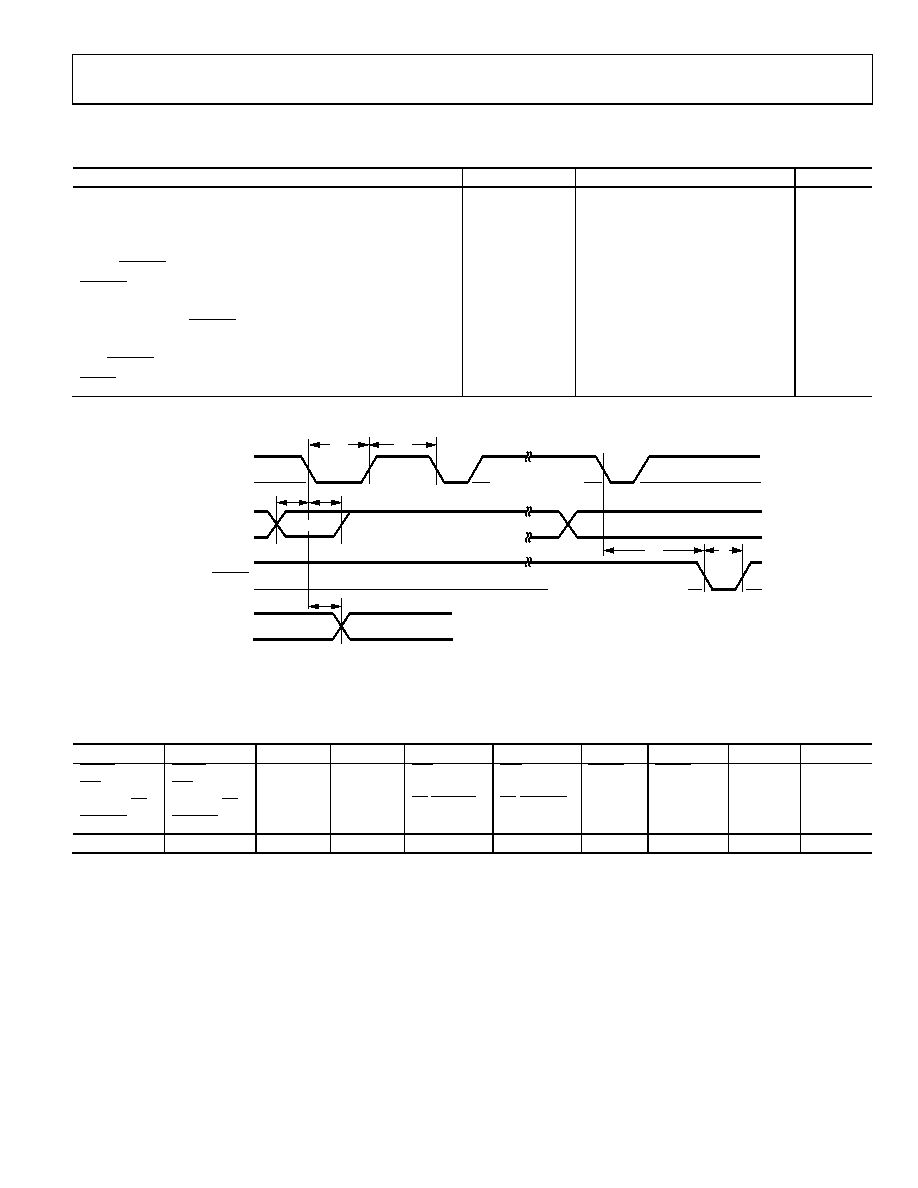

TIMING CHARACTERISTICS (SERIAL)

Table 2.

Parameter

Symbol

Min

Typ

Max

Unit

Serial Data Setup Time

t1

10

ns

CLK Pulse Width

t2

10

ns

Serial Data Hold Time

t3

10

ns

CLK Pulse Separation, Serial Mode

t4

10

ns

CLK to UPDATE Delay

t5

10

ns

UPDATE Pulse Width

t6

10

ns

CLK to DATAOUT Valid, Serial Mode

t7

50

ns

Propagation Delay, UPDATE to Switch On or Off

20

ns

Data Load Time, CLK = 5 MHz, Serial Mode

8

μs

CLK, UPDATE Rise and Fall Times

50

ns

RESET Time

30

ns

Timing Diagram—Serial Mode

LOAD DATA INTO

SERIAL REGISTER

ON FALLING EDGE

1

0

1

0

DATAIN

CLK

1 = LATCHED

0 = TRANSPARENT

DATAOUT

OUT07 (D3)

OUT07 (RESERVED)

OUT00 (D0)

TRANSFER DATA FROM SERIAL

REGISTER TO PARALLEL

LATCHES DURING LOW LEVEL

t7

t1

t3

t6

t2

t4

t5

UPDATE

09

31

8-

0

02

Figure 2. Timing Diagram, Serial Mode

LOGIC LEVELS

Table 3. Logic Levels

VIH

VIL

VOH

VOL

IIH

IIL

IIH

IIL

IOH

IOL

RESET,

SER/PAR, CLK,

DATA IN, CE,

UPDATE

RESET,

SER/PAR, CLK,

DATA IN, CE,

UPDATE

DATA OUT

SER/PAR,

CLK, DATA IN,

CE, UPDATE

SER/PAR,

CLK, DATA IN,

CE, UPDATE

RESET

DATA OUT

2.0 V min

0.8 V max

2.4 V min

0.4 V max

2 μA max

300 μA max

3 mA min

1 mA min

相关PDF资料 |

PDF描述 |

|---|---|

| PIC24HJ64GP210AT-I/PF | IC PIC MCU FLASH 64KB 100-TQFP |

| PIC16C57-LPE/SO | IC MCU OTP 2KX12 28SOIC |

| PIC24HJ128GP306A-E/MR | IC PIC MCU FLASH 128KB 64-QFN |

| DEHR32E222KN2A | CAP CER 2200PF 250V 10% RADIAL |

| DEA1X3F820JN3A | CAP CER 82PF 3.15KV 5% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADV32343001 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV32368102 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV32368601 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV32369201 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV32374302 | 制造商:LG Corporation 功能描述:Frame Assembly |

发布紧急采购,3分钟左右您将得到回复。