- 您现在的位置:买卖IC网 > PDF目录15528 > ADZS-BF537-EZLITE (Analog Devices Inc)BOARD EVAL ADSP-BF537 PDF资料下载

参数资料

| 型号: | ADZS-BF537-EZLITE |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/68页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL ADSP-BF537 |

| 产品培训模块: | Interfacing AV Converters to Blackfin Processors Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services Introduction to VisualDSP++® Tools |

| 特色产品: | Blackfin? BF50x Series Processors |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | DSP |

| 适用于相关产品: | ADSP-BF537 |

| 所含物品: | 评估板、软件和说明文档 |

| 配用: | ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARD ADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE ADZS-USBLAN-EZEXT-ND - BOARD DAUGHTER EXTENDED USB-LAN ADZS-BFFPGA-EZEXT-ND - BOARD EVAL FPGA BLACKFIN EXTENDR |

| 相关产品: | ADSP-BF537KBCZ-6BV-ND - IC DSP CTLR 16BIT 208CSPBGA ADSP-BF537BBCZ-5BV-ND - IC DSP CTLR 16BIT 208CSPBGA ADSP-BF537KBCZ-6AV-ND - IC DSP CTLR 16BIT 182CSPBGA ADSP-BF537BBCZ-5AV-ND - IC DSP CTLR 16BIT 182CSPBGA ADSP-BF537BBCZ-5B-ND - IC DSP CTLR 16BIT 208CSPBGA ADSP-BF537BBC-5A-ND - IC DSP CTLR 16BIT 182CSPBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 24 of 68

|

February 2014

requirements for the ADSP-BF534/ADSP-BF536/ADSP-BF537

processor clocks. Take care in selecting MSEL, SSEL, and CSEL

ratios so as not to exceed the maximum core clock and system

clock. Table 13 describes phase-locked loop operating

conditions.

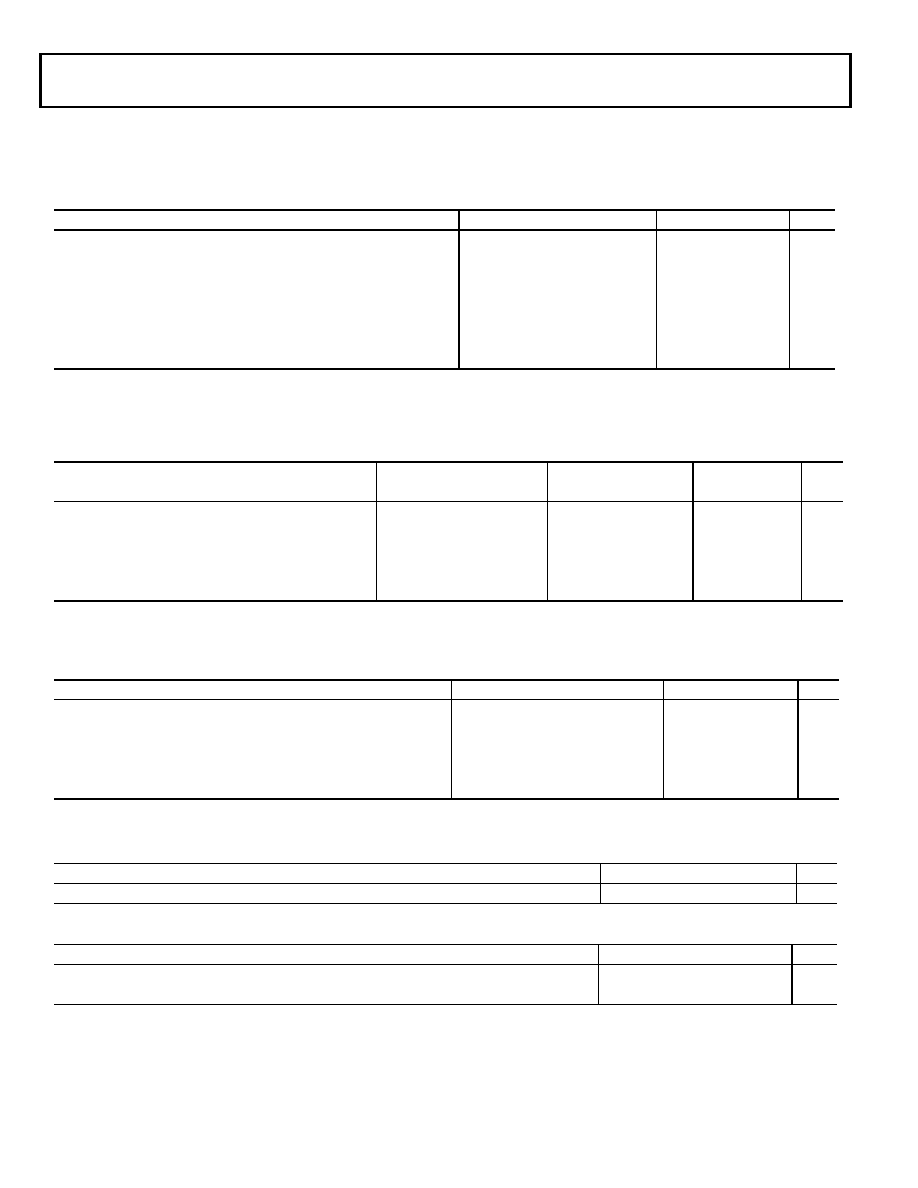

Table 10. Core Clock Requirements—500 MHz, 533 MHz, and 600 MHz Speed Grades1

Parameter

Internal Regulator Setting

Max

Unit

fCCLK

Core Clock Frequency (VDDINT =1.30 V Minimum)

2

1.30 V

600

MHz

fCCLK

Core Clock Frequency (VDDINT = 1.20 V Minimum)

3

1.25 V

533

MHz

fCCLK

Core Clock Frequency (VDDINT =1.14 V Minimum)

1.20 V

500

MHz

fCCLK

Core Clock Frequency (VDDINT =1.045 V Minimum)

1.10 V

444

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.95 V Minimum)

1.00 V

400

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.85 V Minimum)

0.90 V

333

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.8 V Minimum)

0.85 V

250

MHz

1 See Ordering Guide on Page 67.

2 Applies to 600 MHz models only. See Ordering Guide on Page 67.

3 Applies to 533 MHz and 600 MHz models only. See Ordering Guide on Page 67.

Table 11. Core Clock Requirements—400 MHz Speed Grade1

120°C

T

J 105°C

All2 Other TJ

Unit

Parameter

Internal Regulator Setting

Max

fCCLK

Core Clock Frequency (VDDINT =1.14 V Minimum) 1.20 V

400

MHz

fCCLK

Core Clock Frequency (VDDINT =1.045 V Minimum) 1.10 V

333

363

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.95 V Minimum) 1.00 V

295

333

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.85 V Minimum) 0.90 V

280

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.8 V Minimum) 0.85 V

250

MHz

1 See Ordering Guide on Page 67.

Table 12. Core Clock Requirements—300 MHz Speed Grade1

Parameter

Internal Regulator Setting

Max

Unit

fCCLK

Core Clock Frequency (VDDINT =1.14 V Minimum)

1.20 V

300

MHz

fCCLK

Core Clock Frequency (VDDINT =1.045 V Minimum)

1.10 V

255

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.95 V Minimum)

1.00 V

210

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.85 V Minimum)

0.90 V

180

MHz

fCCLK

Core Clock Frequency (VDDINT = 0.8 V Minimum)

0.85 V

160

MHz

1 See Ordering Guide on Page 67.

Table 13. Phase-Locked Loop Operating Conditions

Parameter

Min

Max

Unit

fVCO

Voltage Controlled Oscillator (VCO) Frequency

50

Max fCCLK

MHz

Table 14. System Clock Requirements

Parameter

Condition

Max

Unit

fSCLK

1

VDDEXT 3.3 V or 2.5 V, VDDINT 1.14 V

133

2

MHz

fSCLK

VDDEXT 3.3 V or 2.5 V, VDDINT 1.14 V

100

MHz

1 fSCLK must be less than or equal to fCCLK and is subject to additional restrictions for SDRAM interface operation. See Table 27 on Page 34.

2 Rounded number. Actual test specification is SCLK period of 7.5 ns. See Table 27 on Page 34.

相关PDF资料 |

PDF描述 |

|---|---|

| ECM15DSEI-S243 | CONN EDGECARD 30POS .156 EYELET |

| ADZS-BF518F-EZBRD | BOARD EVAL BF512F/14F/16F/18F |

| ADZS-BF526-EZBRD | BOARD EVAL NO DEBUG BF526 |

| GCM18DTBN-S189 | CONN EDGECARD 36POS R/A .156 SLD |

| GCM18DTBH-S189 | CONN EDGECARD 36POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADZS-BF537-STAMP | 功能描述:SYSTEM DEV FOR ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| ADZS-BF537-STAMP | 制造商:Analog Devices 功能描述:Microcontroller Development Tool |

| ADZS-BF538-EZLITE | 制造商:Analog Devices 功能描述:- Bulk |

| ADZSBF538FEZLITE | 制造商:Analog Devices 功能描述:RES Wirewound 6927 75Ohm 1% 3W 20PPM SMD T/R |

| ADZS-BF538F-EZLITE | 功能描述:BOARD EVAL FOR ADSP-BF538 RoHS:否 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

发布紧急采购,3分钟左右您将得到回复。