- 您现在的位置:买卖IC网 > PDF目录378403 > AN1504D (ON SEMICONDUCTOR) Metastability and the ECLinPS Family PDF资料下载

参数资料

| 型号: | AN1504D |

| 厂商: | ON SEMICONDUCTOR |

| 英文描述: | Metastability and the ECLinPS Family |

| 中文描述: | 亚稳态和业界的EClinPS家庭 |

| 文件页数: | 4/8页 |

| 文件大小: | 135K |

| 代理商: | AN1504D |

AN1504/D

http://onsemi.com

4

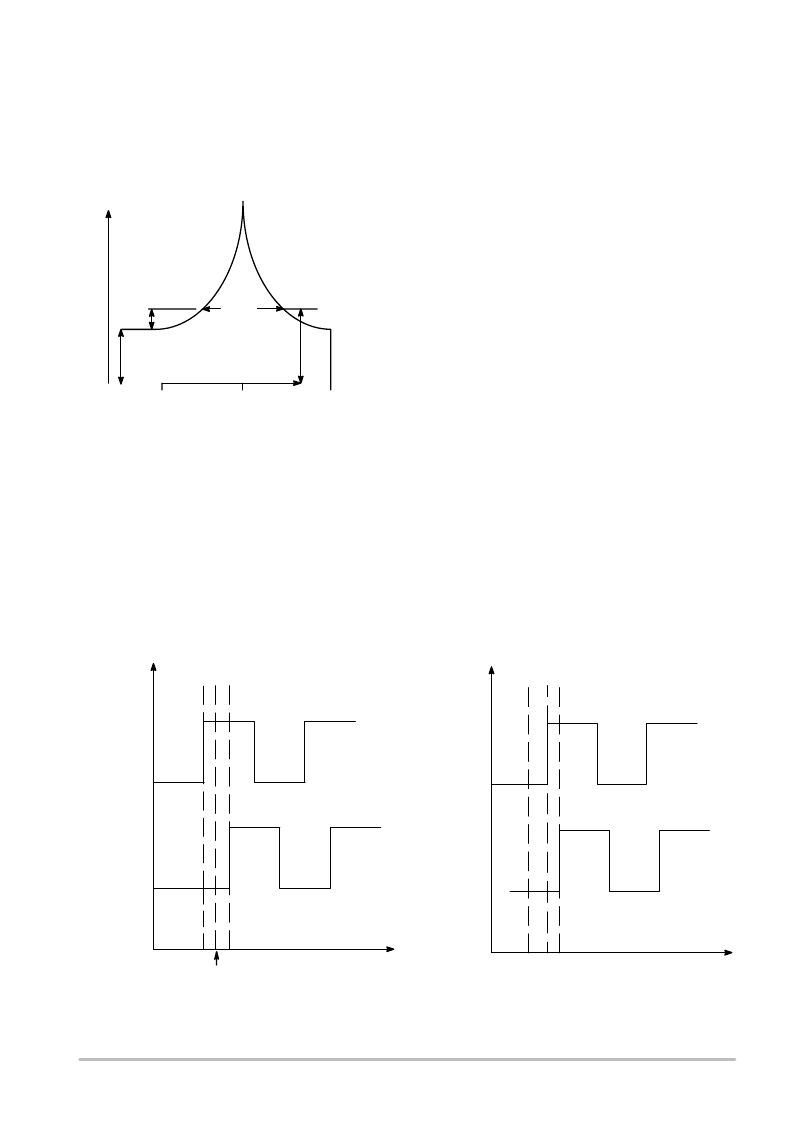

Metastable Equations

Flip

flop propagation delay as a function of the input

signal is represented in Figure 6.

T

D

T

P

T

MAX

T

0

T

F

DATA

INPUT

TIME

Figure 6. Flip

Flop Response Time Plot

P

t

T

W

(T

D

)

The ordinate is the flip

flop propagation delay time, and

the abscissa is the time that data arrives at the flip

flop input

relative to reference time, T

0

. For devices with positive

set

up times T

0

represents the clock transition time with the

difference between T

0

and T

MAX

being the minimum

allowable set

up time. Thus data arriving before time T

MAX

will elicit a nominal propagation delay, T

P

, when clocked.

For data appearing between times T

MAX

and T

F

the

propagation delay will be longer than T

P

because the set

up

and/or hold times have been violated; and the device enters

the metastable state. Data occurring at the input after time T

F

will have no affect on the output, hence the output does not

change and the propagation delay is defined as zero.

For devices with zero or negative set

up times the same

response plot applies, however the abscissa is shifted such

that the value of T0 is no longer the clock transition time.

The same concepts are valid for derivation of metastability

equations for each case: positive, negative or zero set

up

and hold times. To clarify the flip

flop response plot,

Figure 7 illustrates a case in which the propagation delay is

T

P

. Data arrives at time T

A

, allowing the proper set

up time

prior to a clock transition and is maintained at this level for

the specified hold time. Figure 8 is an example in which the

propagation delay is longer than T

P

since the data arrives at

time T

A

, violating the set

up time.

Using the response plot in Figure 6, Stoll

1

developed the

concept of a failure window to facilitate the characterization

of metastability. The value of T

W

(T

D

) is the width of the

window for which a propagation delay of time duration T

D

occurs, and is the range of data input times relative to the

clock input for which a failure will occur. The value of T

D

is the maximum allowable propagation delay; delays longer

than T

D

constitute a failure. The failure window is described

mathematically as:

TW(TD)

TP

10( t) t

(eq. 1)

Where:

T

W

(T

D

) Failure Window Width

T

P

Nominal Propagation Delay

T

D

Delay After Clock That

Constitutes a Failure

Flip

Flop Resolution Time Constant

t

Excess Delay (T

D

T

P

)

T

0

T

MAX

T

A

CLOCK SIGNAL

TIME

DATA SIGNAL

Figure 7. Proper Set

Up and Hold Times

T

0

T

MAX

T

A

CLOCK SIGNAL

DATA SIGNAL

TIME

Figure 8. Violation of Set

Up and Hold Times

相关PDF资料 |

PDF描述 |

|---|---|

| AN1568 | Interfacing Between LVDS and ECL |

| AN1568D | Interfacing Between LVDS and ECL |

| AN1593 | LOW COST 1.0 A CURRENT SOURCE FOR BATTERY CHARGERS |

| AN1607 | ITC122 low voltage micro to motor interface |

| AN1672 | The ECL Translator Guide |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AN15167A-VT | 制造商:Panasonic Industrial Company 功能描述:IC |

| AN1523 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:11W FLYBACK CONVERTER FOR AUXILIARY POWER SUPPLY APPLICATION USING THE L6590 |

| AN1527 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:DEVELOPING A USB SMARTCARD READER WITH ST7SCR |

| AN1549.0 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Addressing Power Issues in Real Time Clock Applications |

| AN155 | 制造商:SILABS 制造商全称:SILABS 功能描述:STEPPER MOTOR REFERENCE DESIGN |

发布紧急采购,3分钟左右您将得到回复。