- 您现在的位置:买卖IC网 > PDF目录166232 > AS7C3364FT36B-65TQCN (INTEGRATED SILICON SOLUTION INC) 64K X 36 STANDARD SRAM, 6.5 ns, PQFP100 PDF资料下载

参数资料

| 型号: | AS7C3364FT36B-65TQCN |

| 厂商: | INTEGRATED SILICON SOLUTION INC |

| 元件分类: | SRAM |

| 英文描述: | 64K X 36 STANDARD SRAM, 6.5 ns, PQFP100 |

| 封装: | 14 X 20 MM, LEAD FREE, TQFP-100 |

| 文件页数: | 2/19页 |

| 文件大小: | 417K |

| 代理商: | AS7C3364FT36B-65TQCN |

AS7C3364FT32B

2/8/05; v.1.2

Alliance Semiconductor

P. 10 of 19

AS7C3364FT36B

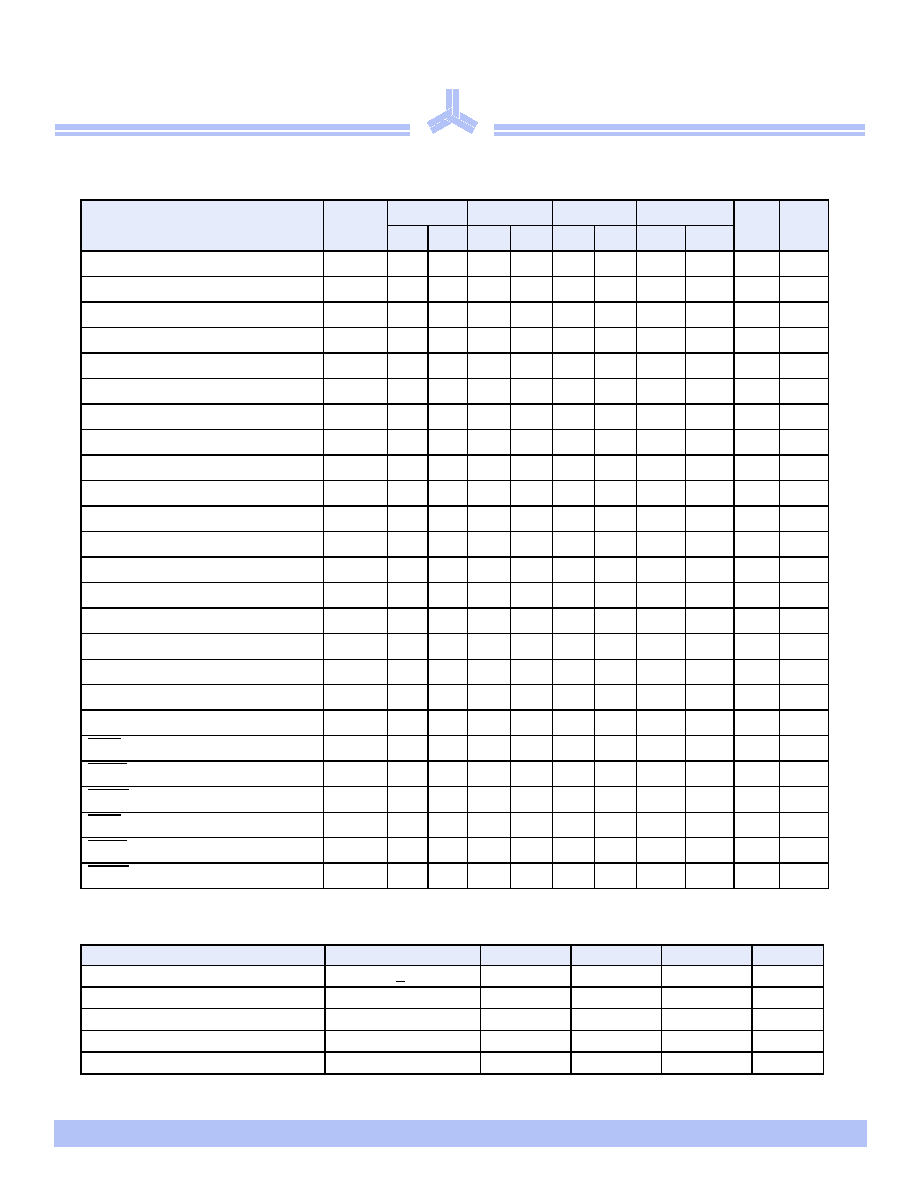

Snooze Mode Electrical Characteristics

Timing characteristics over operating range

Parameter

Sym

–65

-75

-80

–10

Unit

Notes

1

1

Min Max

Min

Max

Min

Max

Min

Max

Cycle time

tCYC

7.5

–

8.5

–

10

–

12

–

ns

Clock access time

tCD

–

6.5

–

7.5

–

8.0

–

10

ns

Output enable LOW to data valid

tOE

–

3.5

–

3.5

–

4.0

–

4.0

ns

Clock HIGH to output Low Z

tLZC

2.5

–

2.5

–

2.5

–

2.5

–

ns

2,3,4

Data output invalid from clock HIGH

tOH

2.5

–

2.5

–

2.5

–

2.5

–

ns

2

Output enable LOW to output Low Z

tLZOE

0

–

0

–

0

–

0

–

ns

2,3,4

Output enable HIGH to output High Z

tHZOE

–

3.0

–

3.5

–

4.0

–

5.0

ns

2,3,4

Clock HIGH to output High Z

tHZC

–

3.0

–

3.5

–

4.0

–

5.0

ns

2,3,4

Output enable HIGH to invalid output

tOHOE

0

–

0

–0–

0

–

ns

Clock HIGH pulse width

tCH

2.5

–

3.0

–

4.0

–

4.0

–

ns

5

Clock LOW pulse width

tCL

2.5

–

3.0

–

4.0

–

4.0

–

ns

5

Address setup to clock HIGH

tAS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6

Data setup to clock HIGH

tDS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6

Write setup to clock HIGH

tWS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6,7

Chip select setup to clock HIGH

tCSS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6,8

Address hold from clock HIGH

tAH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6

Data hold from clock HIGH

tDH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6

Write hold from clock HIGH

tWH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6,7

Chip select hold from clock HIGH

tCSH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6,8

ADV setup to clock HIGH

tADVS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6

ADSP setup to clock HIGH

tADSPS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6

ADSC setup to clock HIGH

tADSCS

1.5

–

2.0

–

2.0

–

2.0

–

ns

6

ADV hold from clock HIGH

tADVH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6

ADSP hold from clock HIGH

tADSPH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6

ADSC hold from clock HIGH

tADSCH

0.5

–

0.5

–

0.5

–

0.5

–

ns

6

Description

Conditions

Symbol

Min

Max

Units

Current during Snooze Mode

ZZ > VIH

ISB2

30

mA

ZZ active to input ignored

tPDS

2cycle

ZZ inactive to input sampled

tPUS

2cycle

ZZ active to SNOOZE current

tZZI

2cycle

ZZ inactive to exit SNOOZE current

tRZZI

0

相关PDF资料 |

PDF描述 |

|---|---|

| AS7C3364FT36B-80TQC | 64K X 36 STANDARD SRAM, 8 ns, PQFP100 |

| AS7C34098-35JC | 256K X 16 STANDARD SRAM, 35 ns, PDSO44 |

| AS7C4098-35JI | 256K X 16 STANDARD SRAM, 35 ns, PDSO44 |

| AS7C3512K16Z-4BC | 512K X 16 ZBT SRAM, 4 ns, PBGA119 |

| AS8863M5-1.8 | 1.8 V FIXED POSITIVE LDO REGULATOR, 0.26 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AS7C3364FT36B-65TQI | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V 64K x 32/36 Flow Through Synchronous SRAM |

| AS7C3364FT36B-65TQIN | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V 64K x 32/36 Flow Through Synchronous SRAM |

| AS7C3364FT36B-75TQC | 制造商:Alliance Semiconductor 功能描述:SRAM Chip Sync Quad 3.3V 2.25M-Bit 64K x 36 7.5ns 100-Pin TQFP |

| AS7C3364FT36B-75TQCN | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V 64K x 32/36 Flow Through Synchronous SRAM |

| AS7C3364FT36B-75TQI | 制造商:ALSC 制造商全称:Alliance Semiconductor Corporation 功能描述:3.3V 64K x 32/36 Flow Through Synchronous SRAM |

发布紧急采购,3分钟左右您将得到回复。