参数资料

| 型号: | BR24S64F-WE2 |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 15/41页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 64KBIT 100KHZ SOP8 |

| 标准包装: | 2,500 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 64K (8K x 8) |

| 速度: | 400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-SOP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

�� �

�

BR24L� □□� -W� Series,BR24S� □□□� -W� Series�

�Technical� Note�

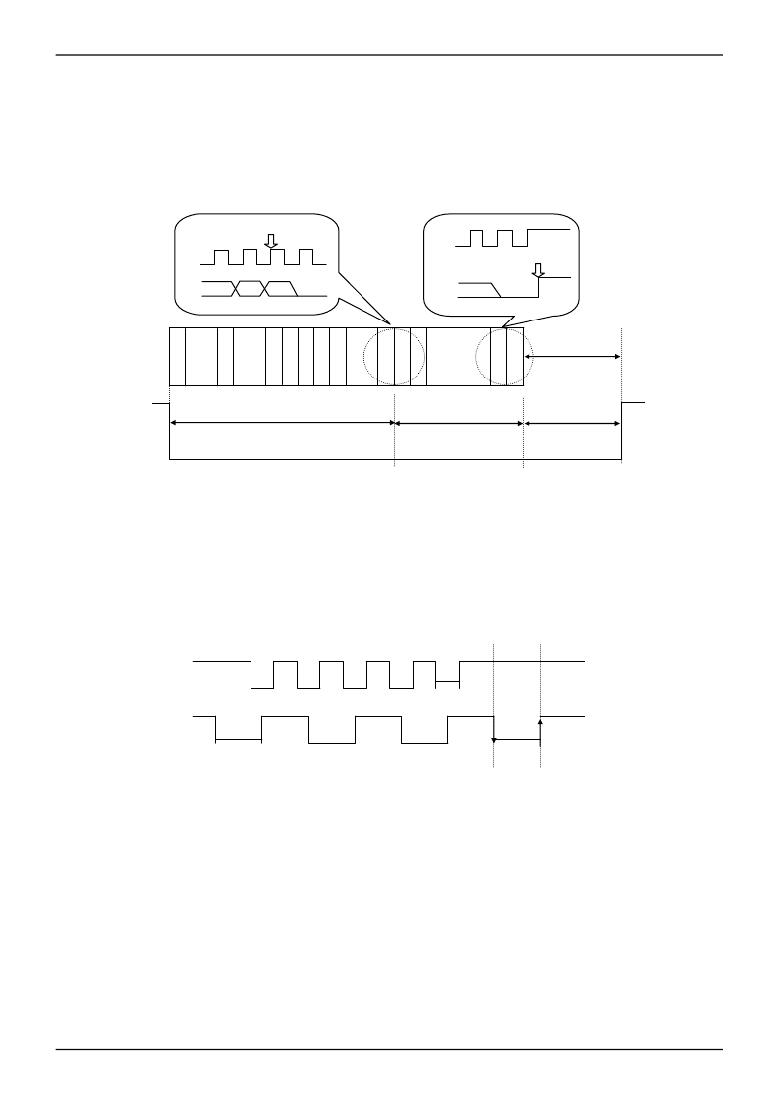

�●� WP� valid� timing� (write� cancel)�

�WP� is� usually� fixed� to� 'H'� or� 'L',� but� when� WP� is� used� to� cancel� write� cycle� and� so� forth,� pay� attention� to� the� following� WP�

�valid� timing.� During� write� cycle� execution,� in� cancel� valid� area,� by� setting� WP='H',� write� cycle� can� be� cancelled.� In� both� byte�

�write� cycle� and� page� write� cycle,� the� area� from� the� first� start� condition� of� command� to� the� rise� of� clock� to� taken� in� D0� of�

�data(in� page� write� cycle,� the� first� byte� data)� is� cancel� invalid� area.�

�WP� input� in� this� area� becomes� Don't� care.� Set� the� setup� time� to� rise� of� D0� taken� SCL� 100ns� or� more.� The� area� from� the� rise�

�of� SCL� to� take� in� D0� to� the� end� of� internal� automatic� write� (tWR)� is� cancel� valid� area.� And,� when� it� is� set� WP='H'� during� tWR,�

�write� is� ended� forcibly,� data� of� address� under� access� is� not� guaranteed,� therefore,� write� it� once� again.� (Refer� to� Fig.50.)� After�

�execution� of� forced� end� by� WP,� standby� status� gets� in,� so� there� is� no� need� to� wait� for� tWR� (5ms� at� maximum).�

�?� Rise� of� D0� taken� clock�

�SCL�

�SCL�

�?� Rise� of� SDA�

�SDA�

�D1�

�D0�

�ACK�

�SDA�

�D0�

�ACK�

�Enlarged� view�

�Enlarged� view�

�SDA�

�S�

�T� Slave�

�A� address�

�R�

�T�

�A�

�C� Word�

�K� address�

�L�

�A�

�C� D7� D6� D5� D4� D3� D2� D1� D0�

�K�

�L�

�A�

�C�

�K�

�L�

�Data�

�A�

�C�

�K�

�L�

�S�

�T�

�O�

�P�

�tWR�

�WP�

�WP� cancel� invalid� area�

�WP� cancel� valid� area�

�Data� is� not� written.�

�Write� forced� end�

�Data� not� guaranteed�

�Fig.50� WP� valid� timing�

�●� Command� cancel� by� start� condition� and� stop� condition�

�During� command� input,� by� continuously� inputting� start� condition� and� stop� condition,� command� can� be� cancelled.�

�(Refer� to� Fig.� 51)�

�However,� in� ACK� output� area� and� during� data� read,� SDA� bus� may� output� 'L',� and� in� this� case,� start� condition� and� stop�

�condition� cannot� be� input,� so� reset� is� not� available.� Therefore,� execute� software� reset.� And� when� command� is� cancelled� by�

�start,� stop� condition,� during� random� read� cycle,� sequential� read� cycle,� or� current� read� cycle,� internal� setting� address� is� not�

�determined,� therefore,� it� is� not� possible� to� carry� out� current� read� cycle� in� succession.� When� to� carry� out� read� cycle� in�

�succession,� carry� out� random� read� cycle.�

�SCL�

�SDA�

�1�

�0�

�1�

�0�

�Start� condition�

�Stop� condition�

�Fig.51� Case� of� cancel� by� start,� stop� condition� during� slave� address� input�

�www.rohm.com�

�?� 2009� ROHM� Co.,� Ltd.� All� rights� reserved.�

�15/40�

�2009.09� -� Rev.D�

�相关PDF资料 |

PDF描述 |

|---|---|

| BR24S64FVM-WTR | IC EEPROM 64KBIT 100KHZ MSOP8 |

| BR24S32NUX-WTR | IC EEPROM 32KBIT 100KHZ VSON8 |

| BR25L160F-WE2 | IC EEPROM SER 16KB SPI BUS 8SOP |

| AT24C128C-SSHM-T | IC EEPROM 128KBIT 400KHZ 8SOIC |

| XC6VLX75T-3FFG484C | IC FPGA VIRTEX 6 74K 484FFGBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BR24S64F-WTR | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24S64NUX-WE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24S64NUX-WTR | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Series EEPROMs I2C BUS |

| BR24S64-W | 制造商:ROHM 制造商全称:Rohm 功能描述:I2C BUS Serial EEPROMs |

| BR24SXX-W | 制造商:ROHM 制造商全称:Rohm 功能描述:I2C BUS Serial EEPROMs |

发布紧急采购,3分钟左右您将得到回复。