- 您现在的位置:买卖IC网 > PDF目录255989 > BU-63825D0-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF资料下载

参数资料

| 型号: | BU-63825D0-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封装: | CERAMIC, DIP-70 |

| 文件页数: | 46/48页 |

| 文件大小: | 405K |

| 代理商: | BU-63825D0-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页

7

Data Device Corporation

www.ddc-web.com

BU-63825

C-02/06-0

hour burn-in (standard on this device), 100% non-destructive

wirebond pull (standard on this device), X-ray analysis, as well

as Destructive Physical Analysis (DPA) testing, extended tem-

perature cycling for QCI testing, and a moisture content limit of

5000 PPM. TABLE 3 summarizes the procurement screening,

element evaluation, and hybrid screening used in the production

of the BU-63825.

ADDRESSING, INTERNAL REGISTERS, AND MEMORY

MANAGEMENT

The software interface of the BU-63825 to the host processor

consists of 17 internal operational registers for normal operation,

an additional 8 test registers, plus 64K X 16 of shared memory

address space. The BU-63825’s 16K X 16 of internal RAM

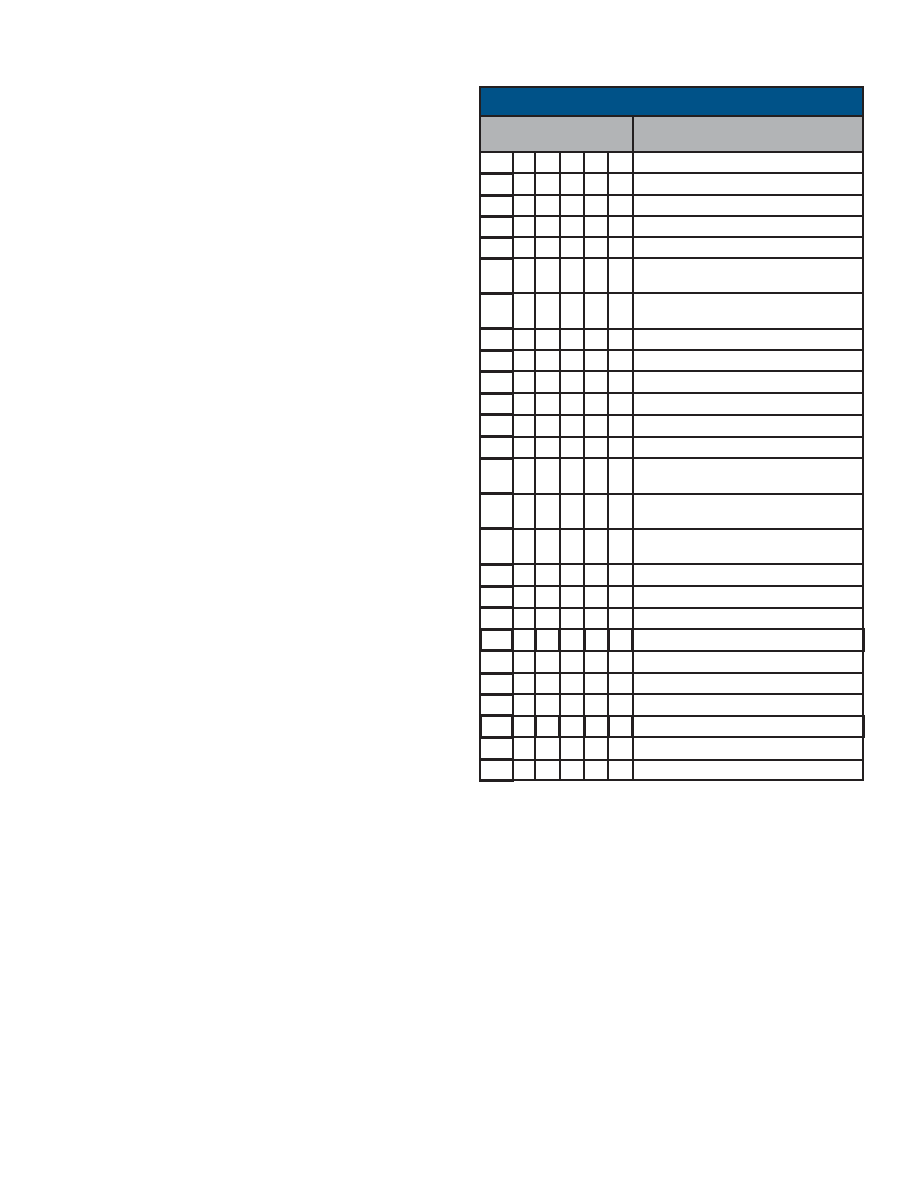

resides in this address space. Reference TABLE 4.

Definition of the address mapping and accessibility for the

Sp’ACE II’s 17 nontest registers, and the test registers, is as fol-

lows:

Interrupt Mask Register:

Used to enable and disable interrupt requests for various condi-

tions.

Configuration Registers #1 and #2:

Used to select the BU-63825’s mode of operation, and for soft-

ware control of RT Status Word bits, Active Memory Area, BC

Stop-on-Error, RT Memory Management mode selection, and

control of the Time Tag operation.

Start/Reset Register:

Used for “command” type functions, such as software reset,

BC/MT Start, Interrupt Reset, Time Tag Reset, and Time Tag

Register Test. The Start/Reset Register includes provisions for

stopping the BC in its auto-repeat mode, either at the end of the

current message or at the end of the current BC frame.

BC/RT Command Stack Pointer Register:

Allows the host CPU to determine the pointer location for the cur-

rent or most recent message when the BU-63825 is in BC or RT

modes.

BC Control Word/RT Subaddress Control Word

Register:

In BC mode, allows host access to the current or most recent BC

Control Word. The BC Control Word contains bits that select the

active bus and message format, enable off-line self-test, mask-

ing of Status Word bits, enable retries and interrupts, and speci-

fy MIL-STD-1553A or -1553B error handling. In RT mode, this

register allows host access to the current or most recent

Subaddress Control Word. The Subaddress Control Word is

reserved

1

1F

reserved

0

1

18

Test Mode Register 7

1

0

1

17

Test Mode Register 0

0

1

10

RT BIT Word Register (RD)

1

0

0F

RT Status Word Register (RD)

0

1

0

0E

BC Frame Time/RT Last Command

/MT Trigger Word Register (RD/WR)

1

0

1

0

0D

BC Time Remaining to Next Message

Register (RD/WR)

0

1

0

0C

BC Frame Time Remaining Register

(RD/WR)

1

0

1

0

0B

Data Stack Address Register (RD/WR)

0

1

0

1

0

0A

Configuration Register #5 (RD/WR)

1

0

1

0

09

Configuration Register #4 (RD/WR)

0

1

0

08

Configuration Register #3 (RD/WR)

1

0

07

Interrupt Status Register (RD)

0

1

0

06

Time Tag Register (RD/WR)

1

0

1

0

05

BC Control Word/RT Subaddress Control

Word Register (RD/WR)

0

1

0

04

BC/RT Command Stack Pointer Register

(RD)

1

0

03

Start/Reset Register (WR)

1

0

03

Configuration Register #2 (RD/WR)

0

1

0

02

Configuration Register #1 (RD/WR)

1

0

01

Interrupt Mask Register (RD/WR)

0

00

A0

A1

A2

A3

A4

HEX

REGISTER

DESCRIPTION/ACCESSIBILITY

ADDRESS LINES

TABLE 4. ADDRESS MAPPING

used to select the memory management scheme and enable

interrupts for the current message. The read/write accessibility

can be used as an aid for testing the Sp’ACE II hybrid.

Time Tag Register:

Maintains the value of a real-time clock. The resolution of this

register is programmable from among 2, 4, 8, 16, 32, and 64

s/LSB. The TAG_CLK input signal also may cause an external

oscillator to clock the Time Tag Register. Start-of-Message

(SOM) and End-of-Message (EOM) sequences in BC, RT, and

相关PDF资料 |

PDF描述 |

|---|---|

| BU-63825D0-301 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-63825D1-191 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-63825D1-200 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-63825D1-201 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-63825D2-190 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-63-9 | 功能描述:测试电夹 White Insul Alligato RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU-63C-0 | 功能描述:测试电夹 Black Insul Alligato RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU-63C-2 | 功能描述:测试电夹 Red Insul Alligator RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU-63C-4 | 功能描述:测试电夹 Yellow Insul Alligat RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU-63C-5 | 功能描述:测试电夹 Green Insul Alligato RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

发布紧急采购,3分钟左右您将得到回复。