- 您现在的位置:买卖IC网 > PDF目录366628 > C9801CY Hex buffer PDF资料下载

参数资料

| 型号: | C9801CY |

| 英文描述: | Hex buffer |

| 中文描述: | CPU系统时钟发生器|的CMOS | SSOP封装| 56PIN |塑料 |

| 文件页数: | 2/11页 |

| 文件大小: | 100K |

| 代理商: | C9801CY |

Low EMI Clock Generator for Pentium II CPU Systems

with Power Management

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07049 Rev. **

05/03/2001

Page 2 of 11

APPROVED PRODUCT

C9801

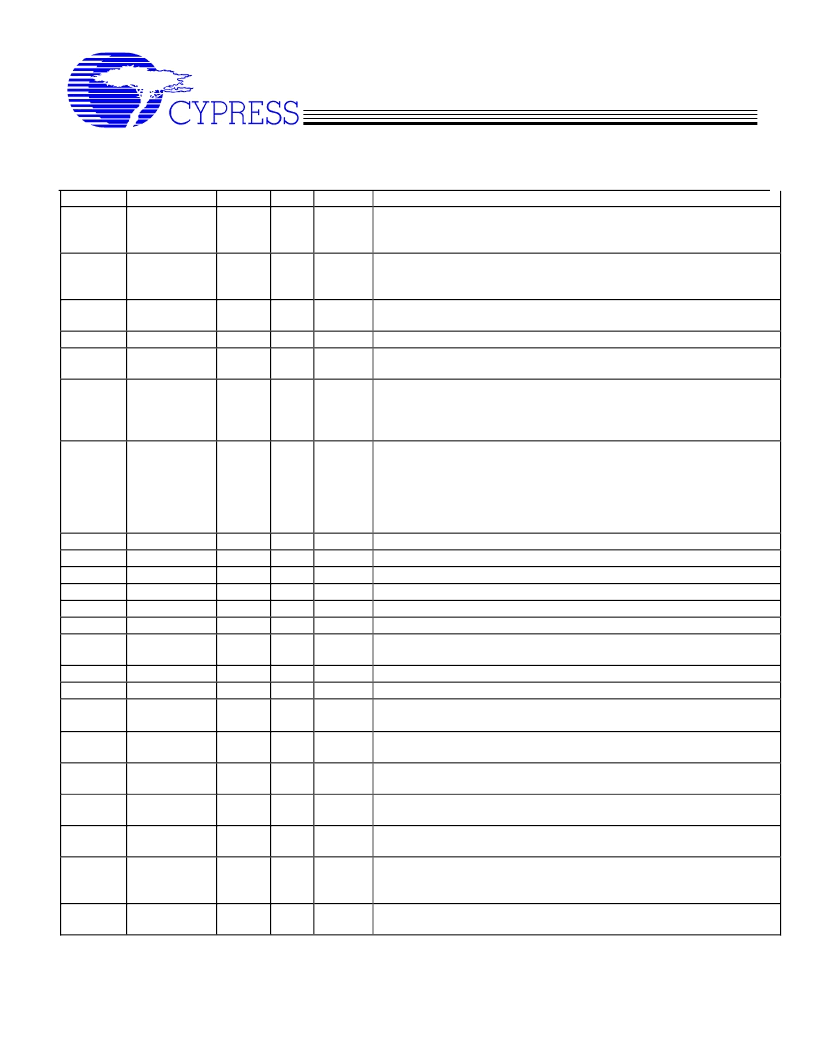

Pin Description

PIN No.

5

Pin Name

Xin

PWR

VDD

I/O

I

TYPE

OSC1

Description

On-chip reference oscillator input pin. Requires either an external

parallel resonant crystal (nominally 14.318 MHz) or externally

generated reference signal

On-chip reference oscillator output pin. Drives an external parallel

resonant crystal when an externally generated reference signal is

used, is left unconnected

Clock outputs. CPU frequency table specified on page 1.

6

Xout

VDD

O

OSC1

41,42,

45,46

49, 50

8

CPU(0:3)

VDDC

0

BUF1

CPU/2 [0,1]

PCI_F

VDDC

VDDP

O

O

BUF4

BUF4

CPU Synchronous clocks. Its frequency is half CPU clocks.

Free running PCI clock. Does not stop when PS# is brought to a

logic 0 (low) level.

PCI bus clocks. See frequency select table on page 1.

9, 11,

12, 14,

15, 17,

18

1, 7,13,

19,20,

24,29,

38, 40,

44,

48,52

10, 16

31

56

43, 47

4, 39

23, 27

21, 22,

25, 26

2,3

30

28

PCI (1:7)

VDDP

O

BUF4

VSS

-

P

-

Ground pins for the device.

VDDP

VDDF

VDDI

VDDC

VDD

VDDA

3V66 (0:3)

-

-

-

-

P

P

P

P

-

-

-

-

3.3 Volt power supply pins for PCI and PCI_F clock output buffers.

3.3 Volt power supply pins for 48 MHz clock output buffers.

2.5 Volt power supply pins for IOAPIC clock buffers.

3.3 or 2.5 Volt power supply pins for CPU clock output buffers.

Power supply pins for analog circuits and core logic.

3.3 Volt power supply pins for 3V66 clock output buffers.

Fixed 66.6 Mhz Advanced Graphics Processor Clock. This clock is

rising edgy synchronous with the CPU clock.

Buffered outputs of on-chip reference oscillator.

Fixed 48 MHz frequency clock output.

CPU frequency select pin.

By design this input does not

contain any internal pull-up or pulldown resistor.

Device power down signal. Removes power from all internal logic

when at a logic low level. See page 4.

PCI clock stop signal. Stops all PCI clocks when at a logic low

level, except for the PCI_F clock. See page 4.

CPU clock stop signal. Stop all CPU clocks when at a logic low

level. See page 4.

Function selector pins. See description on page 3.

-

P

O

-

VDDA

BUF

REF (0:1)

48M

SEL133/

100#

PD#

VDDR

VDDF

-

O

O

I

BUF#

BUF3

PAD

35

PU

37

PS#

PU

36

CS#

PU

32, 33

SEL (0:1)

-

I

PAD

PU

PAD

PU

34

SS#

-

I

When driven to a logic low level, this pin enables the device’s EMI

reducing Spread Spectrum mode (affects only CPU, PCI, 3V66,

and IOAPIC clocks).

2.5 volt copies of a 16.67 Mhz clock that is synchronized with the

CPU clock. See note on page 3

53,54,

55

IOAPIC(0:2)

VDDI

0

PAD

相关PDF资料 |

PDF描述 |

|---|---|

| C9805CYB | Quad line receivers |

| C9811X2AYB | Up to 5A ULDO linear regulator |

| C9812DYB | Up to 5A ULDO linear regulator |

| C9815DY | Up to 5A ULDO linear regulator |

| C9821GQ | Up to 5A ULDO linear regulator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| C9807-832-4 | 制造商:TINNERMAN 功能描述: |

| C980EFN-CTN | 制造商:Thomas & Betts 功能描述:3/4" FSE 1-GANG WP BOX 18 CU IN-CAN |

| C980FFN-CTN | 制造商:Thomas & Betts 功能描述:1" FSE 1-GANG WP BOX 18 CU IN-CAN |

| C9811X2AYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| C9812 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Low EMI Clock Generator for Intel 810E Chipset Systems |

发布紧急采购,3分钟左右您将得到回复。