- 您现在的位置:买卖IC网 > PDF目录366628 > C9822EQ Up to 5A ULDO linear regulator PDF资料下载

参数资料

| 型号: | C9822EQ |

| 英文描述: | Up to 5A ULDO linear regulator |

| 中文描述: | 单时钟驱动器| SSOP封装| 24针|塑料 |

| 文件页数: | 3/19页 |

| 文件大小: | 123K |

| 代理商: | C9822EQ |

Direct Rambus

III Clock Generator

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07093 Rev. **

05/04/2001

Page 3 of 19

APPROVED PRODUCT

C9822

System Clock Configuration

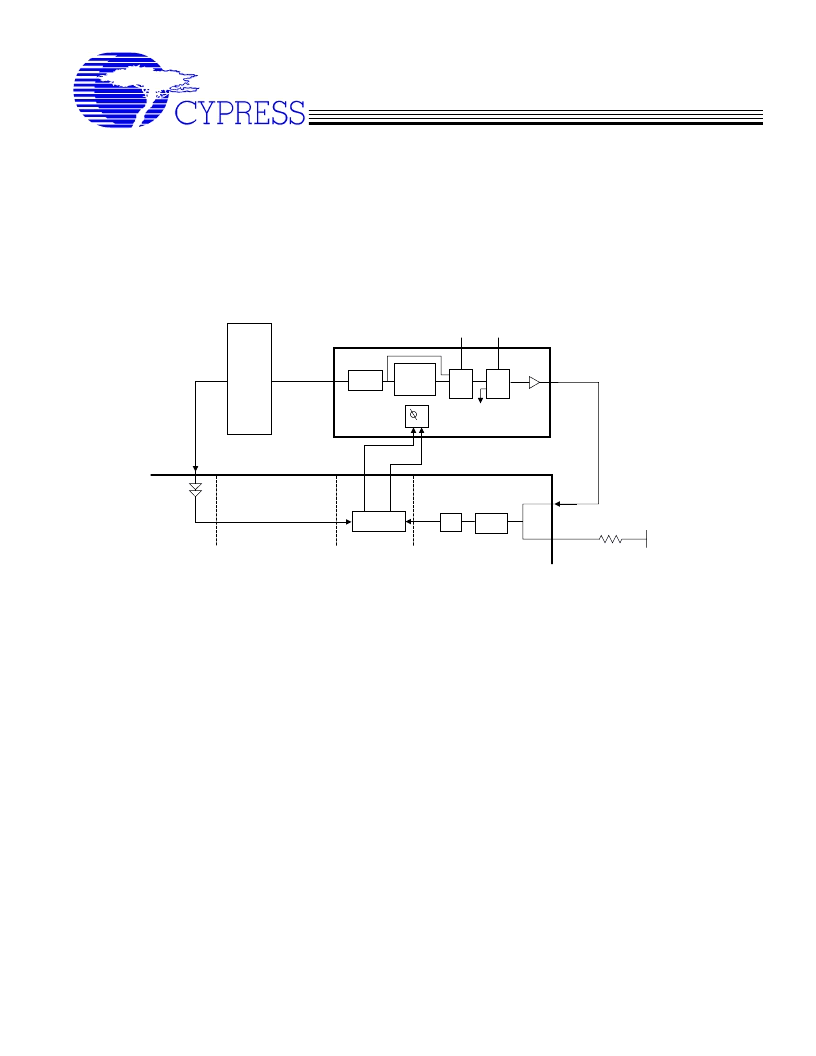

Figure 3 shows the clocking configuration for an example Direct Rambus subsystem. The configuration shows the

interconnection of the system clock source, the C9822, and the clock signals of a memory controller ASIC. The

ASIC contains the RAC, the Rambus Memory Controller protocol engine (RMC), and logic to support

synchronizing the Channel clock with the controller clock (This diagram represents the differential clocks as a

single Busclk wire).

M N

C9801

C9812

C9830

C9840

C9850

C9851

C9853

PLL

Phase

Align

D

C9822

DLL

4

RMC

Pclk

Refclk

S0/S1/S2 STOPB

Busclk

RAC

Synclk

Gear

Ratio

Logic

S

P

Figure: 3 DDLL System Architecture

This configuration achieves frequency-lock between the controller and Rambus Channel clocks (Pclk and Synclk).

these clock signals are matched and phase-aligned at the RMC/RAC boundary in order to allow data transfers to

occur across this boundary without additional latency.

The main clock source drives the system clock (Pclk) to the ASIC, and also drives the reference clock (Refclk) to

the C9822. Refclk is not the same frequency as Pclk. A PLL inside the C9822 multiplies Refclk to generate the

desired frequency for Busclk. Busclk is driven on the Rambus Channel through a terminated transmission line. At

the mid-point of the Channel, the RAC senses Busclk using its own DLL for clock alignment, followed by a fixed

divide-by-4 circuit that generates SynClk.

Pclk is the clock used in the Rambus memory controller (RMC) in the ASIC. SynClk is the clock used at the ASIC

interface of the RAC. the C9822 together with the Gear Ratio Logic enables the controller to exchange data

directly from the Pclk domain to the SynClk domain without incurring additional latency for synchronization. In

general, Pclk and SynClk can run at different frequencies, so the Gear Ratio Logic must select the appropriate M

and N dividers such that the frequencies of Pclk/M and SynClkN are equal. In one example, Pclk = 133 MHz and

SynClk = 100 MHz, and M = 4 while N = 3, giving Pclk/M = SynClk/N = 33 MHz.

The ASIC drives the output clocks, Pclk and SynClk/N from the Gear Ratio Logic to the C9822 Phase Detector

inputs. The routing of the Pclk/M and SynClk/N signal traces must be matched in impedance and propagation

delay on the ASIC as well as on the board. These signals are not part of the Rambus Channel and their routing

must be matched by board designers.

相关PDF资料 |

PDF描述 |

|---|---|

| C9827JT | Up to 5A ULDO linear regulator |

| C9827JY | Up to 5A ULDO linear regulator |

| C9832HT | Up to 5A ULDO linear regulator |

| C9832HY | N-CHANNEL 60V - 0.014 Ohm - 60A TO-220/TO220FP STRIPFET POWER MOSFET |

| C9860-21 | 3 BAND EQUALIZER AUDIO PROCESSOR WITH SUBWOOFER CONTROL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| C98-24379-02 | 制造商:CPI 功能描述: |

| C9827H | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

| C9827HT | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

| C9827HY | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

| C9827JT | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU SYSTEM CLOCK GENERATOR|TSSOP|56PIN|PLASTIC |

发布紧急采购,3分钟左右您将得到回复。