- 您现在的位置:买卖IC网 > PDF目录15139 > CAT1022LI-45-G (ON Semiconductor)IC SUPERVISR CPU 2K EEPROM 8PDIP PDF资料下载

参数资料

| 型号: | CAT1022LI-45-G |

| 厂商: | ON Semiconductor |

| 文件页数: | 10/20页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISR CPU 2K EEPROM 8PDIP |

| 标准包装: | 50 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 130 ms |

| 电压 - 阀值: | 4.5V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-PDIP |

| 包装: | 管件 |

�� �

�

CAT1021,� CAT1022,� CAT1023�

�ACKNOWLEDGE�

�After� a� successful� data� transfer,� each� receiving� device� is�

�required� to� generate� an� acknowledge.� The� acknowledging�

�device� pulls� down� the� SDA� line� during� the� ninth� clock� cycle,�

�signaling� that� it� received� the� 8� bits� of� data.�

�All� devices� respond� with� an� acknowledge� after� receiving�

�a� START� condition� and� its� slave� address.� If� the� device� has�

�When� a� device� begins� a� READ� mode� it� transmits� 8� bits� of�

�data,� releases� the� SDA� line� and� monitors� the� line� for� an�

�acknowledge.� Once� it� receives� this� acknowledge,� the� device�

�will� continue� to� transmit� data.� If� no� acknowledge� is� sent� by�

�the� Master,� the� device� terminates� data� transmission� and�

�waits� for� a� STOP� condition.�

�been� selected� along� with� a� write� operation,� it� responds� with�

�an� acknowledge� after� receiving� each� 8� ?� bit� byte.�

�WRITE� OPERATIONS�

�Byte� Write�

�In� the� Byte� Write� mode,� the� Master� device� sends� the�

�START� condition� and� the� slave� address� information� (with�

�the� R/W� bit� set� to� zero)� to� the� Slave� device.� After� the� Slave�

�generates� an� acknowledge,� the� Master� sends� a� 8� ?� bit� address�

�that� is� to� be� written� into� the� address� pointers� of� the� device.�

�After� receiving� another� acknowledge� from� the� Slave,� the�

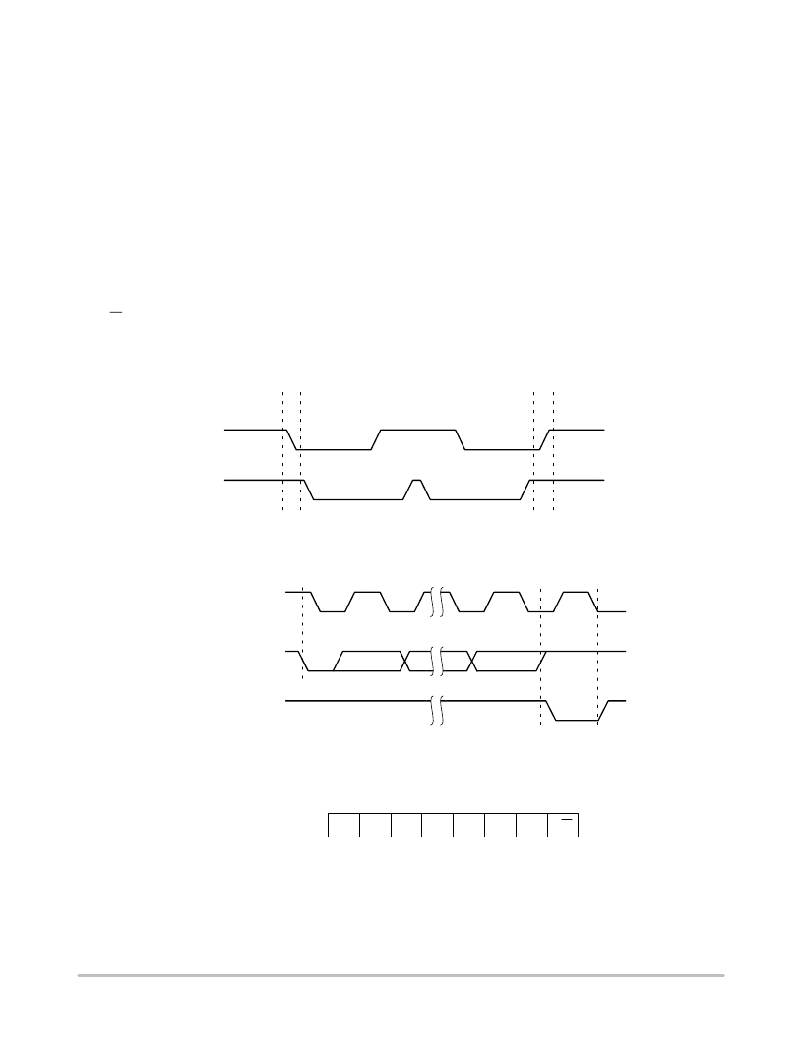

�SD� A�

�SCL�

�START� BIT�

�Master� device� transmits� the� data� to� be� written� into� the�

�addressed� memory� location.� The� device� acknowledges� once�

�more� and� the� Master� generates� the� STOP� condition.� At� this�

�time,� the� device� begins� an� internal� programming� cycle� to�

�non� ?� volatile� memory.� While� the� cycle� is� in� progress,� the�

�device� will� not� respond� to� any� request� from� the� Master�

�device.�

�STOP� BIT�

�Figure� 5.� Start/Stop� Timing�

�SCL� FROM�

�MASTER�

�1�

�8�

�9�

�DATA� OUTPUT�

�FROM� TRANSMITTER�

�DATA� OUTPUT�

�FROM� RECEIVER�

�STA� RT�

�Figure� 6.� Acknowledge� Timing�

�ACKNOWLEDGE�

�Default� Configuration�

�1�

�0�

�1�

�0�

�0�

�0�

�0�

�R/W�

�Figure� 7.� Slave� Address� Bits�

�http://onsemi.com�

�10�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-J4D-EW-F4 | CONVERTER MOD DC/DC 85V 100W |

| VI-J4D-EW-F2 | CONVERTER MOD DC/DC 85V 100W |

| VI-J4D-EW-F1 | CONVERTER MOD DC/DC 85V 100W |

| CAT1024LI-42-G | IC SUPERVISOR W/MEM 4.25V 8DIP |

| VI-J4B-EW-F4 | CONVERTER MOD DC/DC 95V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT1022LI-45-GT2 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022LI-45-GT3 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022LI-45T2 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022LI-45-T2 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022LI-45T3 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

发布紧急采购,3分钟左右您将得到回复。