- 您现在的位置:买卖IC网 > PDF目录223569 > CD40100BDMSR (INTERSIL CORP) 32-BIT BIDIRECTIONAL SERIAL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, CDIP16 PDF资料下载

参数资料

| 型号: | CD40100BDMSR |

| 厂商: | INTERSIL CORP |

| 元件分类: | 计数移位寄存器 |

| 英文描述: | 32-BIT BIDIRECTIONAL SERIAL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, CDIP16 |

| 封装: | BRAZE SEALED, CERAMIC, DIP-16 |

| 文件页数: | 6/9页 |

| 文件大小: | 65K |

| 代理商: | CD40100BDMSR |

1282

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certication.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate

and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

Sales Ofce Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

ASIA

Intersil (Taiwan) Ltd.

Taiwan Limited

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

Specications CD40100BMS

NOTES:

1. Each pin except VDD and GND will have a series resistor of 10K

± 5%, VDD = 18V ± 0.5V

2. Each pin except VDD and GND will have a series resistor of 47K

± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,

VDD = 10V

± 0.5V

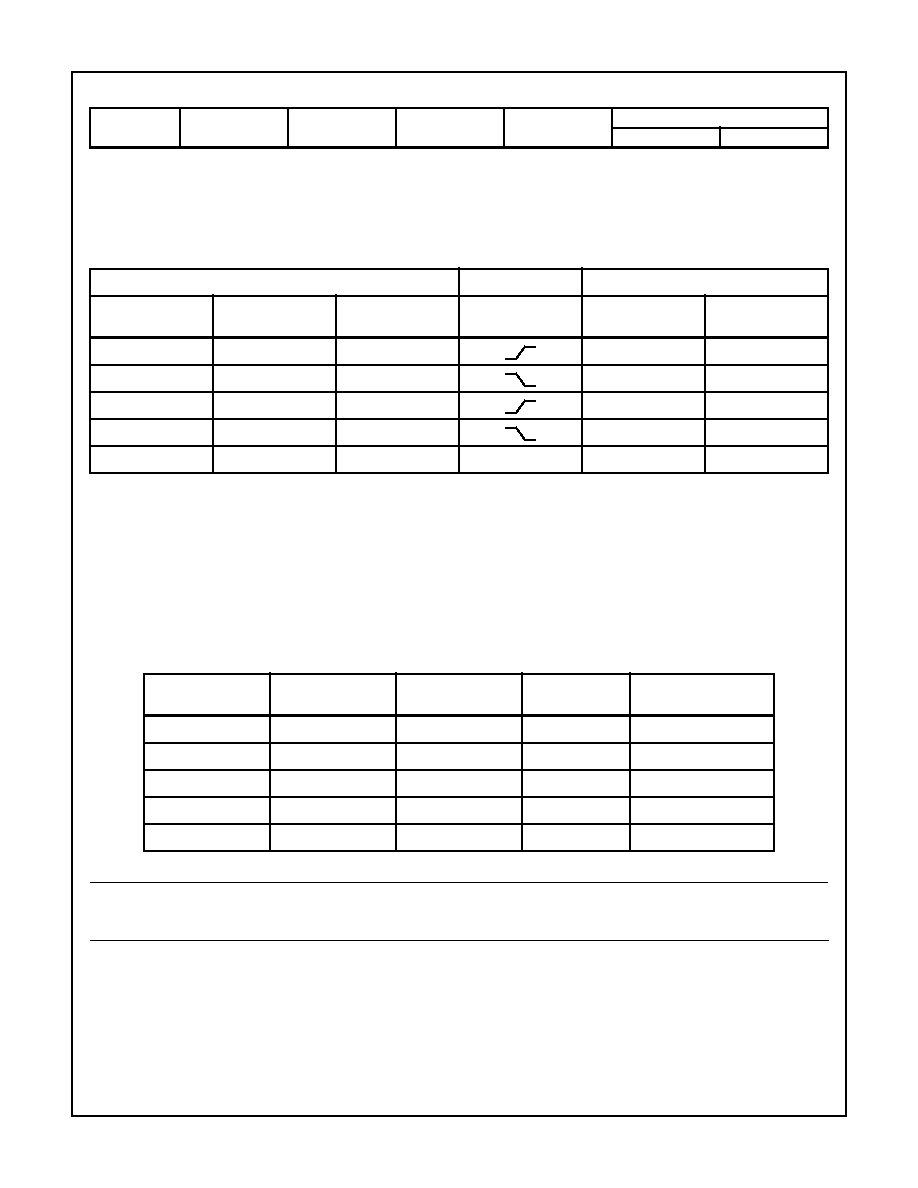

TABLE 9. DATA TRANSFER TABLE*

INITIAL STATE

CLOCK

RESULTING STATE

DATA INPUT

CLOCK INHIBIT

INTERNAL STAGE

LEVEL CHANGE

INTERNAL

STAGE Q

OUTPUT

00

X

0

NC

X0

0

NC

0

10

X

1

NC

X0

1

NC

1

X

1

X

NC

0 = Low Level

1 = High Level

X = Don’t Care

NC = No Change

* For Shift-Right Mode

Data Input = SHIFT RIGHT INPUT (Term. 11)

Internal Stage = Stage 1 (Q1)

Output = SHIFT LEFT OUTPUT (Term. 4)

For Shift Left Mode

Data Input = SHIFT LEFT INPUT (Term. 6)

Internal Stage = Stage 32 (Q32)

Output = SHIFT RIGHT OUTPUT (Term. 12)

TABLE 10. CONTROL TRUTH TABLE

LEFT/RIGHT

CONTROL

CLOCK INHIBIT

RECIRCULATE

CONTROL

ACTION

INPUT BIT ORIGIN

1

0

1

Shift Left

Shift Left Input

1

0

Shift Left

Stage 1

0

1

Shift Right

Shift Right Input

0

Shift Right

Stage 32

X

1

X

No Shift

-

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

(Continued)

FUNCTION

OPEN

GROUND

VDD

9V

± -0.5V

OSCILLATOR

50kHz

25kHz

相关PDF资料 |

PDF描述 |

|---|---|

| CD4015BC | Dual 4-Bit Static Shift Register |

| CD4016BMN | QUAD 1-CHANNEL, SGL POLE SGL THROW SWITCH, PDIP14 |

| CD4023BCJ | Buffered Triple 3-Input NAND,NOR Gate |

| CD4023BCN | Buffered Triple 3-Input NAND,NOR Gate |

| CD4023BC | Buffered Triple 3-Input NAND,NOR Gate |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CD40100BF/3 | 制造商:Harris Corporation 功能描述: |

| CD40100BMS | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS 32-Stage Static Left/Right Shift Register |

| CD40101BD | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| CD40101BFS2225 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CD40101BFX | 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。