- 您现在的位置:买卖IC网 > PDF目录26498 > CDS-1401MM (MURATA POWER SOLUTIONS INC) PDF资料下载

参数资料

| 型号: | CDS-1401MM |

| 厂商: | MURATA POWER SOLUTIONS INC |

| 元件分类: | 取样保持放大器 |

| 中文描述: | SAMPLE AND HOLD AMPLIFIER, 0.35 us ACQUISITION TIME, CDIP24 |

| 封装: | CERAMIC, DDIP-24 |

| 文件页数: | 5/8页 |

| 文件大小: | 87K |

| 代理商: | CDS-1401MM |

5

CDS-1401

track mode when large, high-speed transients (normally

associated with clock edges) are occurring throughout the

system. This could result in the S/H amplifiers being driven

into saturation, and they may not recover in time to accurately

acquire their next signal.

For example, S/H1 should not be commanded into the sample

mode until all transients associated with the opening of the

shunt switch have begun to decay. Similarly, S/H2 should not

be driven into the sample mode until all transients associated

with the clocking of pixel charge onto the output capacitor have

begun to decay. Therefore, it is generally not a good practice

to use the same clock edge to drive S/H1 into hold (holding the

offset) and S/H2 into sample (to acquire the offset + video

signal).

S/H's that are in their signal-acquisition modes should be left

there as long as possible (so all signals can settle) and be

driven into their hold modes before any system transients

occur. In Figure 2, S/H1 is driven into the sample mode shortly

after the transient from the shunt switch has begun to decay.

S/H1 is then kept in the sample mode while the offset signal

and the S/H output settle. S/H1 is driven into hold just prior to

the system clock pulse(s) that transfers the next pixel charge

onto the output capacitor.

As soon as the transients/noise associated with the charge

transport begins to decay, S/H2 can be driven into the sample

mode. S/H2 can then be left in the sample mode until just

before the reset pulse for the output capacitor.

In Figure 2, S/H's 1 and 2 both have the same acquisition time.

If the pixel-to-pixel amplitude variation of offset signals is much

package so they can be used to control other circuit functions.

Each S/H has two pins for offset adjusting (if required), one for

current and one for voltage.

In normal operation, the output signal of the CCD is applied

simultaneously to the inputs (pins 3 and 4) of both S/H

amplifiers. S/H1 will normally be used to capture and hold

each pixel’s offset signal. Therefore, S/H1 is initially in its

signal-acquisition mode (logic “1” applied to pin 11, S/H1

COMMAND). This is also called the sample or track mode.

Following a brief interval during which the output of the CCD

and the output of S/H1 are allowed to settle, S/H1 is driven into

its hold mode by applying a logic “0” to pin 11. S/H1 is now

holding the pixel’s offset value.

In most straightforward configurations, the output of S/H1 is

connected to the summing node of S/H2 by connecting pin 7

(S/H1 ROUT) to pin 8 (S/H2 SUMMING NODE).

When the offset+video signal appears at the output of the

CCD, S/H2 is driven into its signal acquisition mode by

applying a logic “1” to pin 12 (S/H2 COMMAND).

S/H2 employs a current-summing architecture that subtracts

the output of S/H1 (the offset) from the output of the CCD

(offset+video) while acquiring only the difference signal (i.e.,

the valid video). A logic “0” subsequently applied to pin 12

drives S/H2 into its hold mode, and after a brief transient

settling time, the valid video signal appears at pin 22 (V OUT).

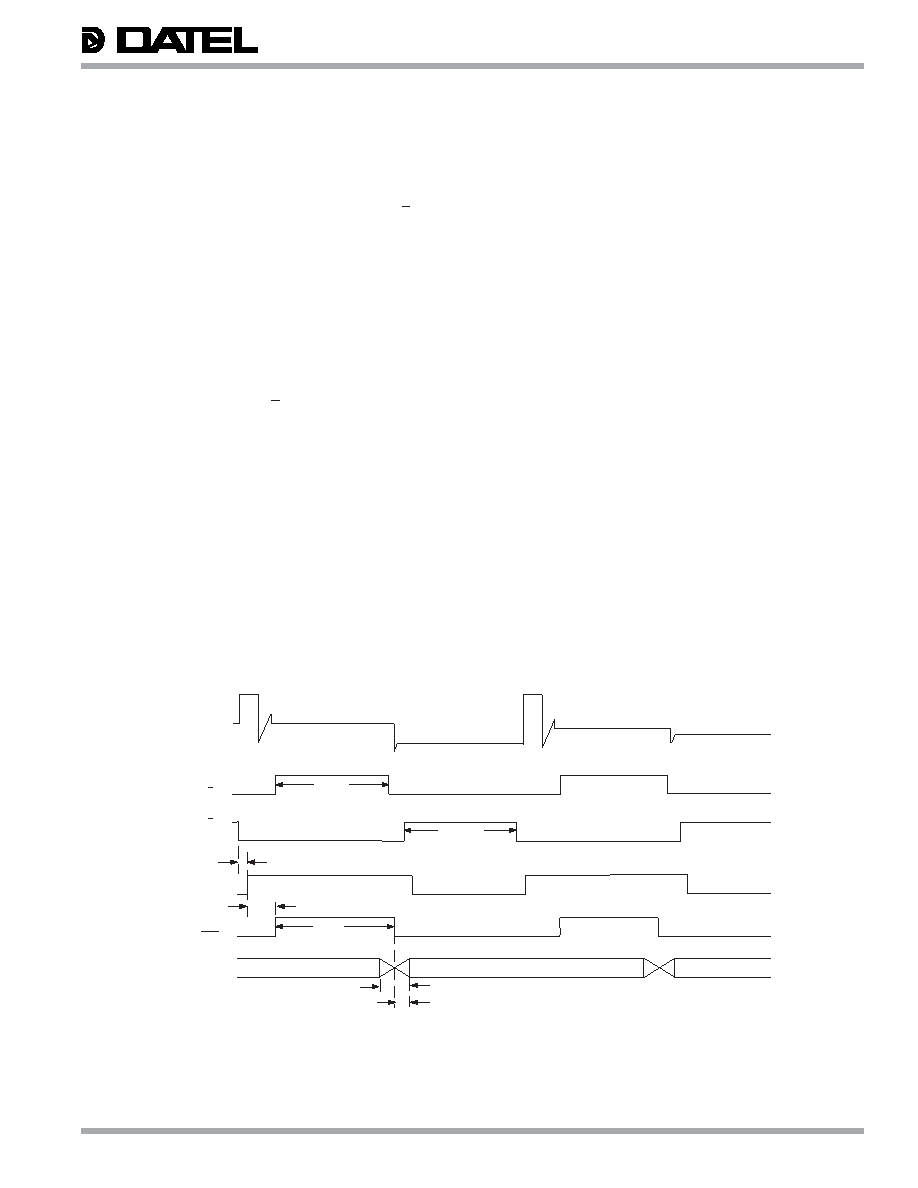

Timing Notes

See Figure 2, Typical Timing Diagram. It is advisable that

neither of the CDS-1401's S/H amplifiers be in their sample/

Figure 3. CDS-1401 in Front of ADS-CCD1201 at f

CLK = 1MHz

S/H1

S/H2

START CONVERT

EOC

OUTPUT

DATA

DATA N-1 VALID

DATA N VALID

30ns typ.

90ns typ.

73ns max.

35ns max.

ANALOG INPUT

FOR CDS

(Pins 3 and 4 are tied)

(CCD OUTPUT)

DATA N+1 VALID

400ns

OFFSET (N+1)

OFFSET +

VIDEO (N+1)

OFFSET (N+2)

OFFSET +

VIDEO (N+2)

420ns

RESET

相关PDF资料 |

PDF描述 |

|---|---|

| CDS-1402MC | |

| CFUKF455KB4X-R0 | |

| CFUKF455KD1X-R0 | |

| CFULB455KB2A-B0 | |

| CFULB455KF4A-B0 | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDS1402 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:14-Bit, Very Fast Settling Correlated Double Sampling Circuit |

| CDS-1402 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:14-Bit, Very Fast Settling Correlated Double Sampling Circuit |

| CDS-1402MC | 制造商:Murata Power Solutions 功能描述:Correlated Double Sampler (Cds) 24-Pin CDDIP |

| CDS-1402MM | 制造商:Murata Power Solutions 功能描述:Correlated Double Sampler (Cds) 24-Pin CDDIP |

| CDS14N | 功能描述:SOCKET,1/4" DRIVE,7MM,6PT 制造商:apex tool group 系列:* 零件状态:在售 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。