- 您现在的位置:买卖IC网 > PDF目录378798 > CDS-1402MC (Electronic Theatre Controls, Inc.) 14-Bit, Very Fast Settling Correlated Double Sampling Circuit PDF资料下载

参数资料

| 型号: | CDS-1402MC |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 14-Bit, Very Fast Settling Correlated Double Sampling Circuit |

| 中文描述: | 14位,非常快速沉降相关双采样电路 |

| 文件页数: | 6/8页 |

| 文件大小: | 203K |

| 代理商: | CDS-1402MC |

CDS -1402

6

As soon as the transients/noise associated with the charge

transport begins to decay, S/H2 can be driven into the sample

mode. S/H2 can then be left in the sample mode until just

before the reset pulse for the output capacitor.

In Figure 2, S/H's 1 and 2 both have the same acquisition time.

If the pixel-to-pixel amplitude variation of offset signals is much

less than that of video signals, it may not be necessary for the

allocated acquisition time of S/H1 to be as long as that of S/H2.

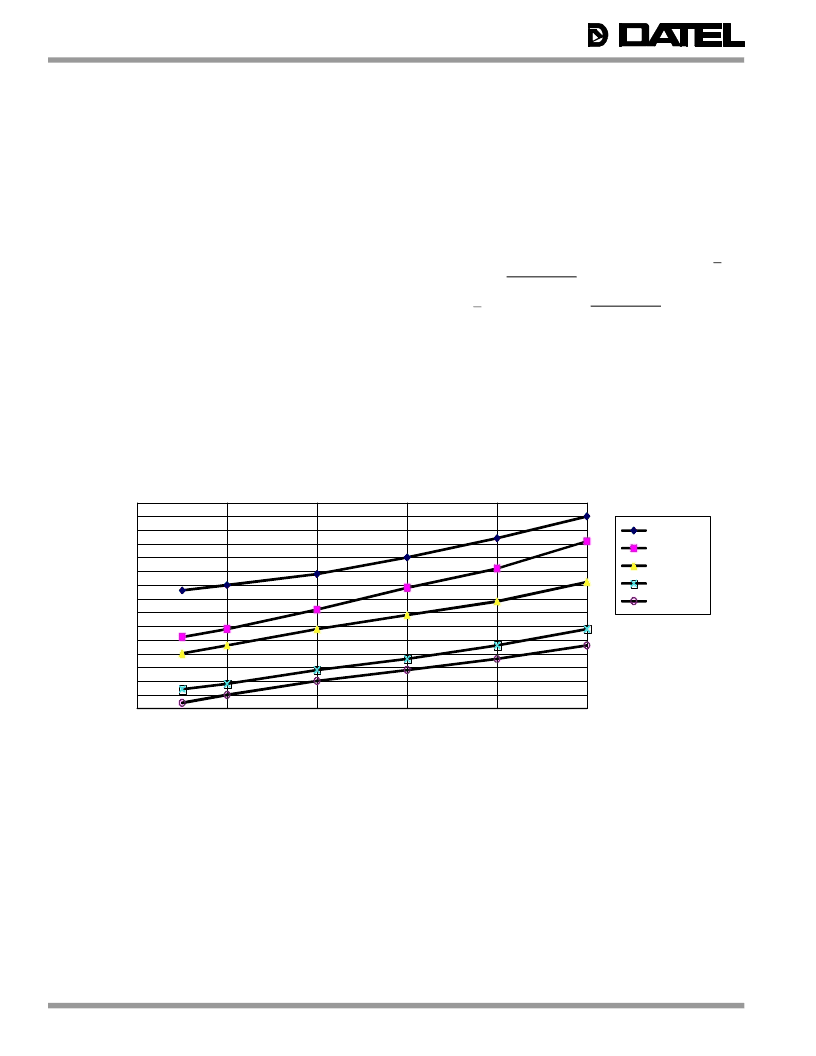

As shown in the plot (Figure 4) of acquisition times vs. input

signal step size, the S/H's internal to the CDS-1402 acquire

smaller-amplitude signals quicker than they acquire larger-

amplitude signals. In "maximum-throughput" applications,

assuming "asymmetric" timing can be accommodated, each

S/H should only be given the time it requires, and no more, to

acquire its input signal. Leaving a S/H amp in the sample

mode for a longer period of time has little added benefit.

As an example, the graph shows that it takes 32ns to acquire a

500mV step to within 10mV of accuracy and 73ns to acquire a

500mV step to within 0.5mV of accuracy. The figures in this

graph are typical values at room temperature.

The CDS-1402 brings out 4 control lines that can be used to

trigger an A/D converter connected to its output. If the A/D is a

30

35

40

45

50

55

60

65

70

75

80

85

90

95

100

105

A

c

q

u

i

s

i

t

i

o

n

T

i

m

e

(

n

s

)

1mV accuracy

2mV accuracy

5mV accuracy

10mV accuracy

Input Step Size (Volts)

A

0

1

2

3

4

5

±0.5mV accuracy

Figure 4. Acquisition Time versus Accuracy and Step Size

sampling type, system timing should be such that the A/D's

input S/H amplifier is acquiring the output of the CDS-1402 at

the same time the output is settling to its final value.

For most sampling A/D's, the rising edge of the start-convert

pulse drives the internal S/H into the hold mode under the

assumption the S/H has already fully acquired and is tracking

the input signal. In this case, the same edge can not be used

to drive S/H2 into the hold mode and simultaneously initiate

the A/D conversion. The output of S/H2 needs time to settle its

sample-to-hold switching transient, and the input S/H of the

A/D needs time to fully acquire its new input signal.

As shown in Figure 1, output line A/D CLOCK1 (pin 18) is a

slightly delayed version of the signal applied to pin 11 (S/H1

COMMAND), and A/D CLOCK1 (pin 17) is its complement.

A/D CLOCK2 (pin 19) is a delayed version of the signal applied

to pin 12 (S/H2 COMMAND), and A/D CLOCK2 (pin 20) is its

complement. Any one of these signals, as appropriate, may be

used to trigger the A/D conversion.

Figure 3 is a typical timing diagram for a CDS-1402 in front of

DATEL's 14-bit, 5MHz sampling A/D, the ADS-944.

相关PDF资料 |

PDF描述 |

|---|---|

| CDS-1402 | 14-Bit, Very Fast Settling Correlated Double Sampling Circuit |

| CDS-1402MM | 14-Bit, Very Fast Settling Correlated Double Sampling Circuit |

| CDS15FD331J03 | Miniature Dipped, Mica Capacitors |

| CDS15CD180J03 | Miniature Dipped, Mica Capacitors |

| CDS15ED200J03 | Miniature Dipped, Mica Capacitors |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDS-1402MM | 制造商:Murata Power Solutions 功能描述:Correlated Double Sampler (Cds) 24-Pin CDDIP |

| CDS14N | 功能描述:SOCKET,1/4" DRIVE,7MM,6PT 制造商:apex tool group 系列:* 零件状态:在售 标准包装:1 |

| CDS15 | 功能描述:保险丝 CARTRIDGE D 15A RoHS:否 制造商:Littelfuse 产品:Surface Mount Fuses 电流额定值:0.5 A 电压额定值:600 V 保险丝类型:Fast Acting 保险丝大小/组:Nano 尺寸:12.1 mm L x 4.5 mm W 安装风格: 端接类型:SMD/SMT 系列:485 |

| CDS150 | 功能描述:保险丝 CNDIAN D-TYP 600V TD RoHS:否 制造商:Littelfuse 产品:Surface Mount Fuses 电流额定值:0.5 A 电压额定值:600 V 保险丝类型:Fast Acting 保险丝大小/组:Nano 尺寸:12.1 mm L x 4.5 mm W 安装风格: 端接类型:SMD/SMT 系列:485 |

| CDS-15118B | 功能描述:8 Ohm Magnetic Speaker 700mW 20Hz ~ 20kHz Top Rectangular 86dB 制造商:cui inc. 系列:CDS 零件状态:有效 类型:磁性 频率范围:20Hz ~ 20kHz 阻抗:8 欧姆 声压级:86dB 功率 - 额定值:700mW 功率 - 最大值:1W 端口位置:顶部 形状:矩形 材料 - 锥体:PET 材料 - 磁铁:Nd-Fe-B 端接:焊盘 大小/尺寸:15.00mm 长 x 11.00mm 宽 高度:3.10mm 标准包装:100 |

发布紧急采购,3分钟左右您将得到回复。