参数资料

| 型号: | CORE1553BBC-AR |

| 厂商: | Microsemi SoC |

| 文件页数: | 10/30页 |

| 文件大小: | 0K |

| 描述: | IP MODULE CORE1553 BUS CTLR |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�Core1553BBC� MIL-STD-1553B� Bus� Controller�

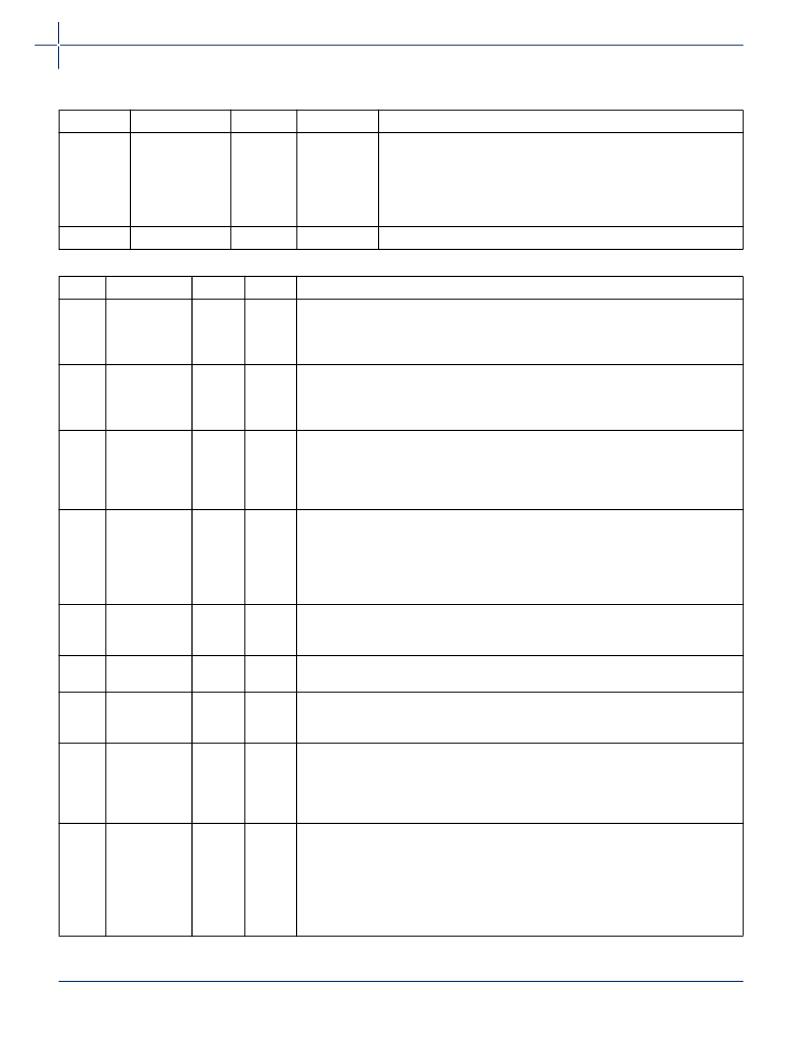

�Table� 8� ?� Bus� Controller� Registers�

�Address�

�110�

�Name�

�STACKPTR�

�Type�

�RW�

�Size�

�[15:0]�

�Function�

�BC� stack� pointer�

�This� is� the� internal� stack� pointer� register;� it� is� used� for� the� CALL� and�

�RETURN� instructions.� When� the� bus� controller� is� started,� the� STACKPTR�

�is� set� to� FFFF.� The� upper� eight� bits� are� fixed� to� FF,� and� the� lower� eight�

�bits� will� count� down� and� up.� This� allows� up� to� 255� addresses� to� be�

�stored� in� the� stack� memory.�

�111�

�INTERRUPT�

�RW�

�[15:0]�

�Interrupt� Register�

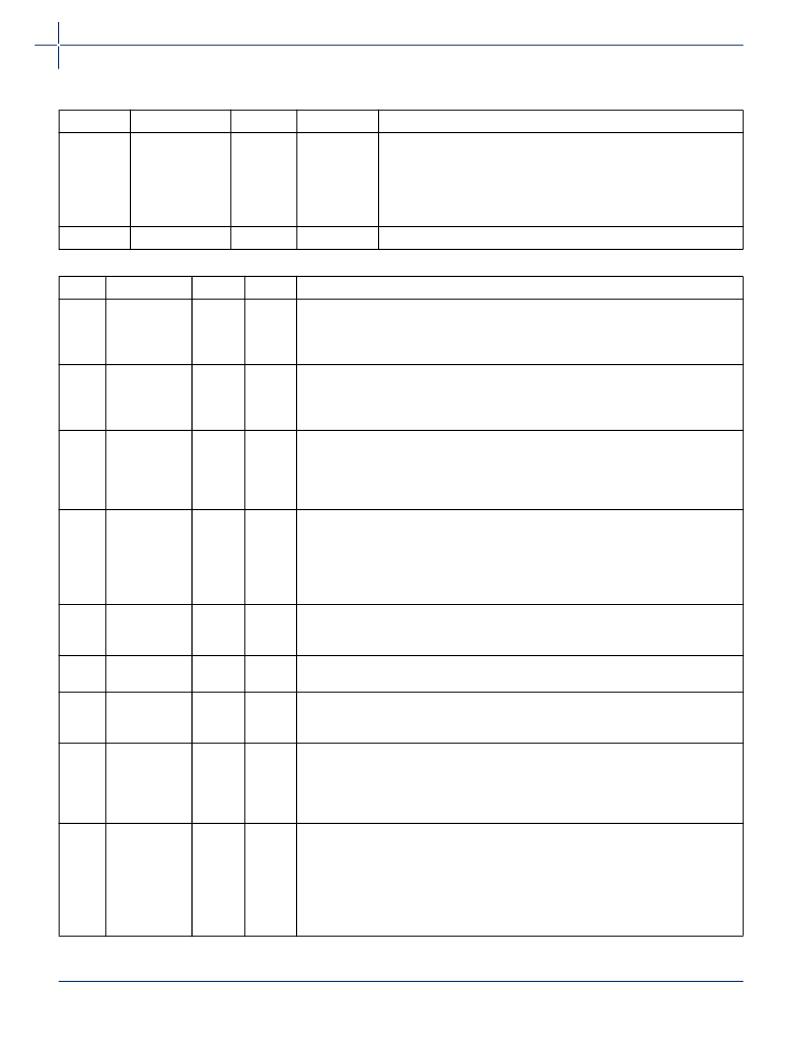

�Table� 9� ?� Setup� Register�

�Bits�

�15�

�Name�

�FORCEORUN�

�Type�

�RW�

�Reset�

�0�

�Function�

�'1':� If� a� BC-RT� message� with� a� word� count� between� 1� and� 31� is� carried� out,� the� BC� will�

�transmit� for� greater� than� 680μs.� This� will� cause� the� transmitter� timer� to� trigger� and� the�

�BC� to� shutdown.�

�'0':� Normal� operation�

�14�

�CLOCKEN�

�RW�

�0�

�Enables� the� internal� CLOCK� to� count�

�'0':� Internal� CLOCK� will� not� count�

�'1':� Internal� CLOCK� enabled�

�The� clock� is� automatically� enabled� by� the� WAITC� instruction.�

�13:12�

�CLKFREQ�

�RW�

�01�

�Tells� the� core� what� the� external� clock� frequency� is�

�00:� 12� MHz�

�01:� 16� MHz�

�10:� 20� MHz�

�11:� 24� MHz�

�11�

�RETRYMODE�

�WR�

�0�

�Sets� how� the� retry� system� works�

�'0':� Retries� on� the� same� bus� for� the� number� of� times� set� by� the� reties� setting� in� the�

�message� block,� then� on� the� alternate� bus� for� the� number� of� times� set� by� the� alternate�

�bus� reties� in� the� message� block.�

�'1':� Reties� alternates� between� the� two� buses.� The� total� number� of� retries� is� the� number�

�of� reties� plus� alternative� bus� retries� as� set� in� the� message� block.�

�10�

�INTENABLE�

�RW�

�0�

�Enables� the� external� interrupt� pin�

�'1':� The� INTPENDING� bit� will� drive� the� INTOUT� pin�

�'0':� The� INTOUT� pin� is� held� at� a� '0'�

�9�

�AUTOCLOCK�

�RW�

�1�

�'1':� Sets� the� CLOCK� register� to� 0000� when� the� BC� is� started�

�'0':� The� CLOCK� register� is� not� reset� when� the� BC� is� started�

�8�

�AUTOSTACK�

�RW�

�1�

�'1':� Sets� the� STACKPTR� register� to� FFFF� when� the� BC� is� started�

�'0':� The� STACKPTR� register� is� not� reset� when� the� BC� is� started.� This� allows� the� BC� to� be�

�restarted� when� previously� stopped.�

�7:6�

�CLKRATE�

�RW�

�00�

�Sets� the� rate� at� which� the� TIMER� and� CLOCK� count�

�00:� 1� μ� s�

�01:� 4� μ� s�

�10:� 8� μ� s�

�11:� 32� μ� s�

�5:4�

�IMG�

�RW�

�00�

�Sets� the� default� minimum� inter-message� GAP�

�00:� 4� μ� s�

�01:� 8� μ� s�

�10:� 16� μ� s�

�11:� 32� μ� s�

�Note:� The� actual� inter-message� GAP� is� a� function� of� the� memory� access� times.� Typically,�

�six� memory� accesses� need� to� take� place� in� the� inter-message� gap.�

�10�

�v4.0�

�相关PDF资料 |

PDF描述 |

|---|---|

| CORE1553BRT-AR | IP MODULE CORE1553 REMOTE TERM |

| CORE8051-AR | IP MODULE CORE8051 |

| COREFFT-RM | IP MODULE COREFFT |

| COREFIR-RM | IP MODULE COREFIR |

| COREPCIF-RM | IP MODULE COREPCIF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE1553BBC-UR | 制造商:Microsemi Corporation 功能描述:SOFTWARE - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE1553BRM-AN | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-AR | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-OM | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-OMFL | 功能描述:IP MODULE CORE1553 BUS/REMOTE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。