参数资料

| 型号: | CORE1553BBC-AR |

| 厂商: | Microsemi SoC |

| 文件页数: | 7/30页 |

| 文件大小: | 0K |

| 描述: | IP MODULE CORE1553 BUS CTLR |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�Core1553BBC� MIL-STD-1553B� Bus� Controller�

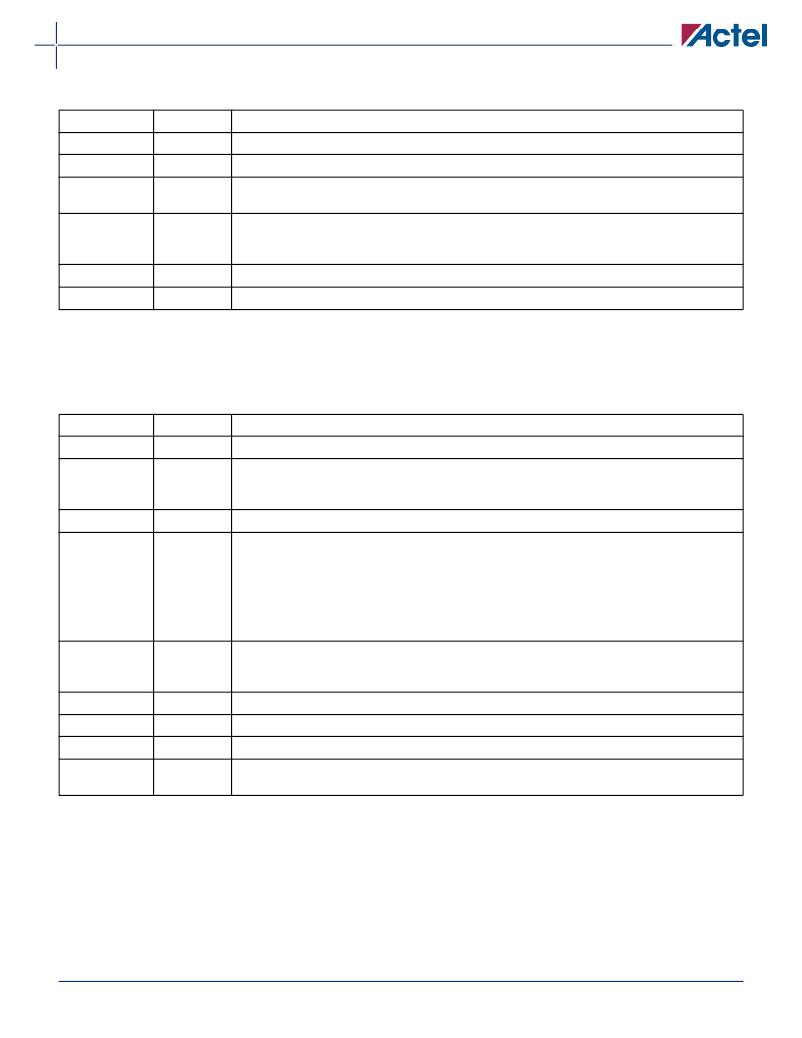

�Table� 3� ?� Control� and� Status� Signals�

�Name�

�CLK�

�RSTINn�

�INTOUT�

�MEMFAIL�

�BUSY�

�EXTFLAG�

�Type�

�In�

�In�

�Out�

�Out�

�Out�

�In�

�Description�

�Master� clock� input� (either� 12� MHz,� 16� MHz,� 20� MHz,� or� 24� MHz)�

�Reset� input� (active� low)�

�Interrupt� Request� (active� high).� The� CPU� is� required� to� read� the� internal� status� register� to� find� the�

�reason� for� the� interrupt.� It� is� cleared� by� the� CPU� writing� to� the� interrupt� register.�

�This� goes� high� if� the� core� fails� to� read� or� write� data� to� the� backend� interface� within� the� required�

�time.� This� can� be� caused� by� the� backend� not� asserting� MEMGNTn� fast� enough� or� asserting�

�MEMWAITn� for� too� long.� It� is� cleared� by� the� CPU� writing� to� the� interrupt� register.�

�This� is� high� when� the� core� is� active,� i.e.� processing� a� message� list.�

�External� flag� input� used� by� the� condition� codes� within� the� bus� controller�

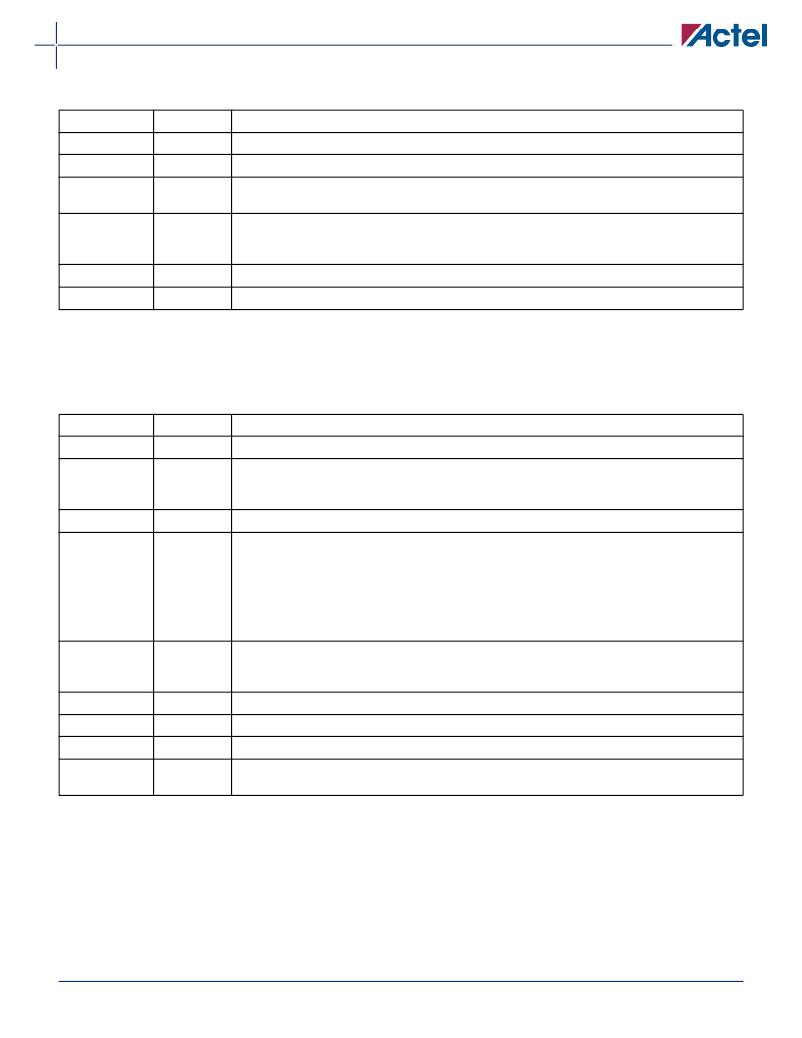

�CPU� Interface�

�The� CPU� interface� allows� access� to� the� Core1553BBC� internal� registers� and� direct� access� to� the� backend� memory.� This�

�interface� is� synchronous� to� the� clock� (� Table� 4� ).�

�Table� 4� ?� CPU� Interface� Signals�

�Name�

�CPUCSn�

�CPUWRn[1:0]�

�CPURDn�

�CPUWAITn�

�CPUMEM�

�CPUADDR[15:0]�

�CPUDOUT[15:0]�

�CPUDIN[15:0]�

�CPUDEN�

�Type�

�In�

�In�

�In�

�Out�

�In�

�In�

�Out�

�In�

�Out�

�Description�

�CPU� chip� select� input� (active� low)�

�CPU� write� input� (active� low).� Two� write� inputs� are� provided� for� processors� that� support� byte�

�operations.� When� CPUWRn[1]� is� '0,'� data� bits� [15:8]� are� written.� When� CPUWRn[0]� is� '0,'� data� bits�

�[7:0]� are� written.�

�CPU� read� input� (active� low)�

�CPU� wait� output� (active� low)� indicates� that� the� CPU� should� hold� CPURDn� or� CPUWRn� active� while�

�the� core� completes� the� read� or� write� operation.� CPUWAITn� is� not� asserted� when� the� internal� CPU�

�registers� are� accessed.� When� accessing� the� backend� interface� through� the� core,� CPUWAIT� will� be�

�activated� for� a� minimum� of� four� clock� cycles� for� read� operations� and� three� for� write� operations.�

�CPUWAITn� is� asserted� for� extra� clock� cycles� if� the� backend� interface� delays� asserting� MEMGNTn� or�

�asserts� MEMWAITn.�

��Selects� whether� the� CPU� accesses� internal� registers� or� backend� memory.�

�'0':� Accesses� internal� registers,� register� number� is� specified� on� CPUADDR[2:0]�

�'1':� Accesses� the� backend� memory�

�CPU� address� input�

�CPU� data� output�

�CPU� data� input�

�Data� bus� enable� (active� high).� This� signal� is� high� when� the� core� is� providing� data� output� on� the�

�CPUDOUT� bus.� It� is� intended� for� a� tristate� enable� function.�

�v4.0�

�7�

�相关PDF资料 |

PDF描述 |

|---|---|

| CORE1553BRT-AR | IP MODULE CORE1553 REMOTE TERM |

| CORE8051-AR | IP MODULE CORE8051 |

| COREFFT-RM | IP MODULE COREFFT |

| COREFIR-RM | IP MODULE COREFIR |

| COREPCIF-RM | IP MODULE COREPCIF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE1553BBC-UR | 制造商:Microsemi Corporation 功能描述:SOFTWARE - Virtual or Non-Physical Inventory (Software & Literature) |

| CORE1553BRM-AN | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-AR | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-OM | 功能描述:IP MODULE CORE1553 BUS/REMOTE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRM-OMFL | 功能描述:IP MODULE CORE1553 BUS/REMOTE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。