参数资料

| 型号: | CS4205-KQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 59/81页 |

| 文件大小: | 0K |

| 描述: | IC CODEC AC97 I2S 48-LQFP |

| 标准包装: | 250 |

| 类型: | 音频编解码器 '97 |

| 数据接口: | 串行 |

| 分辨率(位): | 18,20 b |

| ADC / DAC 数量: | 1 / 2 |

| 三角积分调变: | 是 |

| 动态范围,标准 ADC / DAC (db): | 90 / 90 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-TQFP(9x9) |

| 包装: | 托盘 |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 其它名称: | 598-1182 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页

CS4205

62

DS489PP4

11. CLOCKING

The CS4205 may be operated as a primary or sec-

ondary codec. As a primary codec, the system

clock for the AC-link may be generated from an ex-

ternal 24.576 MHz clock source, a 24.576 MHz

crystal, or the internal Phase Locked Loop (PLL).

The PLL allows the CS4205 to accept external

clock frequencies other than 24.576 MHz. As a

secondary codec, the system clock is derived from

BIT_CLK, which is generated by the primary co-

dec. The CS4205 uses the presence or absence of a

valid clock on the XTL_IN pin in conjunction with

the state of the ID[1:0]# pins to determine the

clocking configuration. See Table 27 for all avail-

able CS4205 clocking modes.

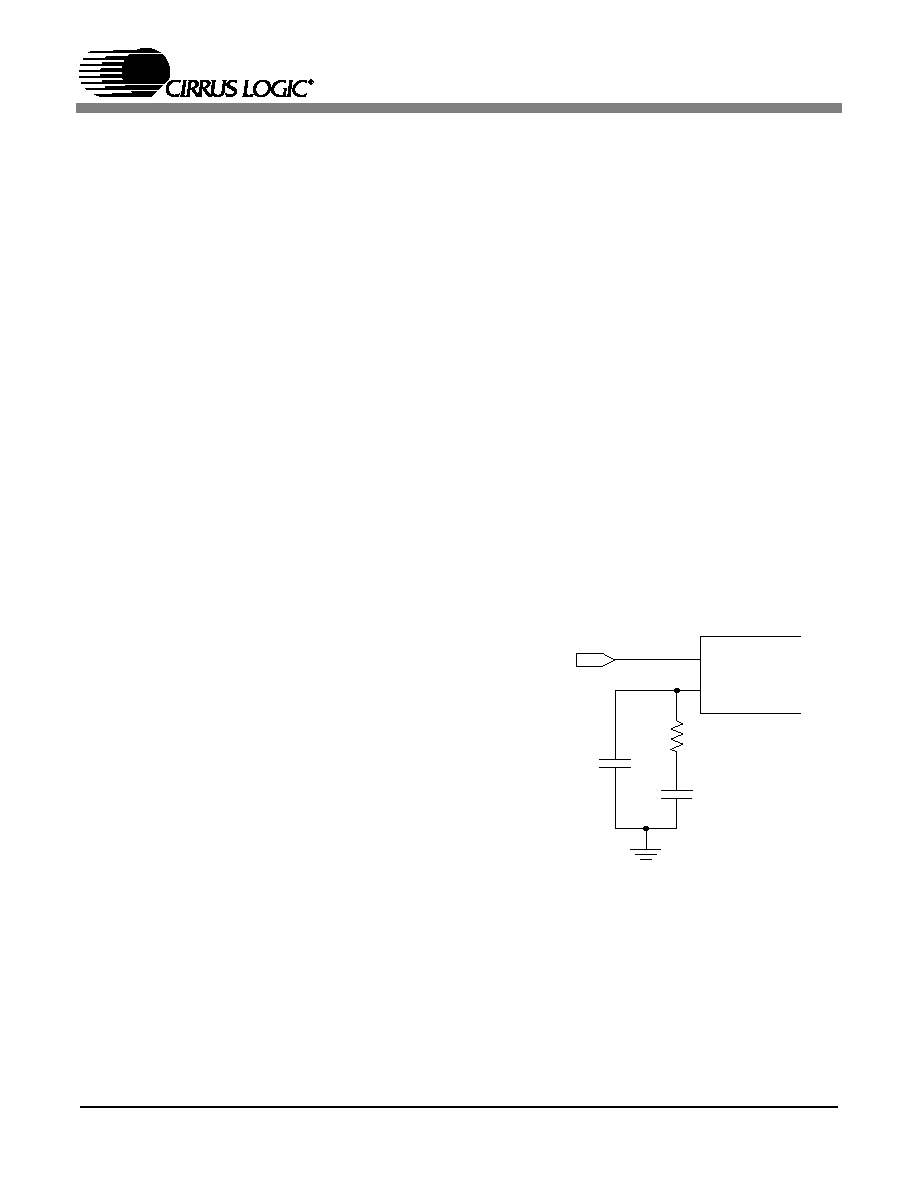

11.1

PLL Operation (External Clock)

The PLL mode is activated if a valid clock is

present on XTL_IN before the rising edge of

RESET#. Once PLL mode is entered, the

XTL_OUT pin is redefined as the PLL loop filter,

as shown in Figure 23. The ID[1:0]# inputs deter-

mine the configuration of the internal divider ratios

required to generate the 12.288 MHz BIT_CLK

output; see Table 27 on page 63 for additional de-

tails. In PLL mode, the CS4205 is configured as a

primary codec independent of the state of the

ID[1:0]# pins. If 24.576 MHz is chosen as the ex-

ternal clock input (ID[1:0]# inputs both pulled high

or left floating), the PLL is disabled and the clock

is used directly. The loop filter is not required and

XTL_OUT is left unconnected. For all other clock

input choices, the loop filter is required. The

ID[1:0] bits of the Extended Audio ID Register

(Index 28h) and the Extended Modem ID Register

(Index 3Ch) will always report ‘00’ in PLL mode.

11.2

24.576 MHz Crystal Operation

If a valid clock is not present on XTL_IN during

the rising edge of RESET#, the device disables the

PLL input and latches the state of the ID[1:0]# in-

puts. If the ID[1:0]# inputs are both pulled high or

left floating, the device is configured as a primary

codec. An external 24.576 MHz crystal is used as

the system clock as shown in Figure 24.

11.3

Secondary Codec Operation

If a valid clock is not present on XTL_IN and either

ID[1:0]# input is pulled low during the rising edge

of RESET#, the device is determined to be a sec-

ondary codec. The BIT_CLK pin is configured as

an input and the CS4205 is driven from the

12.288 MHz BIT_CLK of the primary codec. The

ID[1:0] bits of the Extended Audio ID Register

(Index 28h) and the Extended Modem ID Register

(Index 3Ch) will report the state of the ID[1:0]#

inputs.

Figure 23. PLL External Loop Filter

XTL_OUT

XTL_IN

2.2 k

0.022 uF

220 pF

Clock Source

DGND

相关PDF资料 |

PDF描述 |

|---|---|

| CS4207-DNZ | IC CODEC AUD HDPN AMP AUTO 48QFN |

| CS4265-CNZ | IC CODEC 24BIT 104DB 32QFN |

| CS4270-DZZ | IC CODEC 24BIT 105DB 24TSSOP |

| CS4271-DZZ | IC CODEC 24BIT 114DB 28-TSSOP |

| CS4272-DZZ | IC CODEC 24BIT 114DB 28-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4205-KQZR | 功能描述:接口—CODEC IC AC’97 Codec for Docking Stations RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4207 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, 4-in / 6-out HD Audio CODEC with Headphone Amp |

| CS4207-CNZ | 功能描述:接口—CODEC IC Lo Pwr,4/6 HD Aud Codec w/HP Amp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4207-CNZ/C1 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power, 4-in / 6-out HD Audio CODEC with Headphone Amp |

| CS4207-CNZR | 功能描述:接口—CODEC IC Lo Pwr,4/6 HD Aud Codec w/HP Amp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。