- 您现在的位置:买卖IC网 > PDF目录380066 > CS4210VJG (NATIONAL SEMICONDUCTOR CORP) IEEE 1394 OHCI Controller PDF资料下载

参数资料

| 型号: | CS4210VJG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE 1394 OHCI Controller |

| 中文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | LQFP-100 |

| 文件页数: | 16/102页 |

| 文件大小: | 1571K |

| 代理商: | CS4210VJG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

www.national.com

16

Revision 1.0

G

Operational Description

(Continued)

3.2

There are three basic means by which software communi-

cates with the CS4210: registers, DMA, and interrupts.

SOFTWARE INTERFACE OVERVIEW

3.2.1

The host architecture (PCI, for example) is responsible for

mapping the CS4210’s registers into a portion of the host’s

address space.

Registers

3.2.2

DMA transfers in the CS4210 are accomplished through

one of two methods: DMA memory and physical response

DMA.

DMA Operation

3.2.2.1

DMA memory resident data structures are used to describe

lists of data buffers. The CS4210 automatically sequences

through this buffer descriptor list. This data structure also

contains status information regarding the transfers. Upon

completion of each data transfer, the DMA controller condi-

tionally updates the corresponding DMA context command

and conditionally interrupts the processor so it can observe

the status of the transaction. A set of registers within the

CS4210 is used to initialize each DMA context and to per-

form control actions such as starting the transfer.

DMA Memory

3.2.2.2

The CS4210 can be programmed to accept 1394 read and

write transactions as reads and writes to host memory

space. In this mode, the CS4210 acts as a bus bridge from

the 1394 bus into host memory. The formats for the data

sent and received in all these modes are specified in the

1394 Open Host Controller Interface Specification Release

1.00.

Physical Response DMA

3.2.3

When any DMA transfer completes (or aborts), an interrupt

may be sent to the host system. In addition to the interrupt

Interrupts

sources which correspond to each DMA context comple-

tion, there is also a set of interrupts which correspond to

other CS4210 functions/units. For example, one of these

interrupts could be sent when a Self-ID packet stream has

been received. The processor interrupt line is controlled by

the IntEvent and IntMask registers. The IntEvent register

indicates which interrupt events have occurred, and the Int-

Mask register is used to enable selected interrupts. Soft-

ware writes to the IntEventClear register to clear interrupt

conditions in IntEvent. In addition, there are registers used

by the isochronous transmit and isochronous receive con-

trollers to indicate interrupt conditions for each context.

Table 3-3 shows a map of the IntEvent and IntMask Set/

Clear registers. Refer to Section 4.4.16.1 "IntEvent Regis-

ter" on page 70 and Section 4.4.16.3 "IntMask Register" on

page 72 for further information details.

3.2.3.1

Each asynchronous DMA context has one interrupt indica-

tion bit in the IntEvent register. For requests, it is the reqTx-

Complete bit and for responses it is the respTxComplete

bit. This interrupt indication bit is set to one if a completed

OUTPUT_LAST command has the “i” field set to 11b, or if

the “i” field is set to 01b and transmission of the packet did

not yield an ack_complete or an ack_pending.

Asynchronous Transmit Interrupts

3.2.3.2

There are two interrupts for each context (request and

response) that software can use to gauge the usage of the

receive buffers. If software needs to be informed of the

arrival of each packet being sent to the context buffers, it

can use the RQPkt or RSPkt interrupts in the IntEvent reg-

ister. If software needs to be informed of the completion of

a buffer, it can set the descriptor i field to 11b, which trig-

gers either the ARRQ or ARRS interrupt in the IntEvent

register.

Asynchronous Receive Interrupts

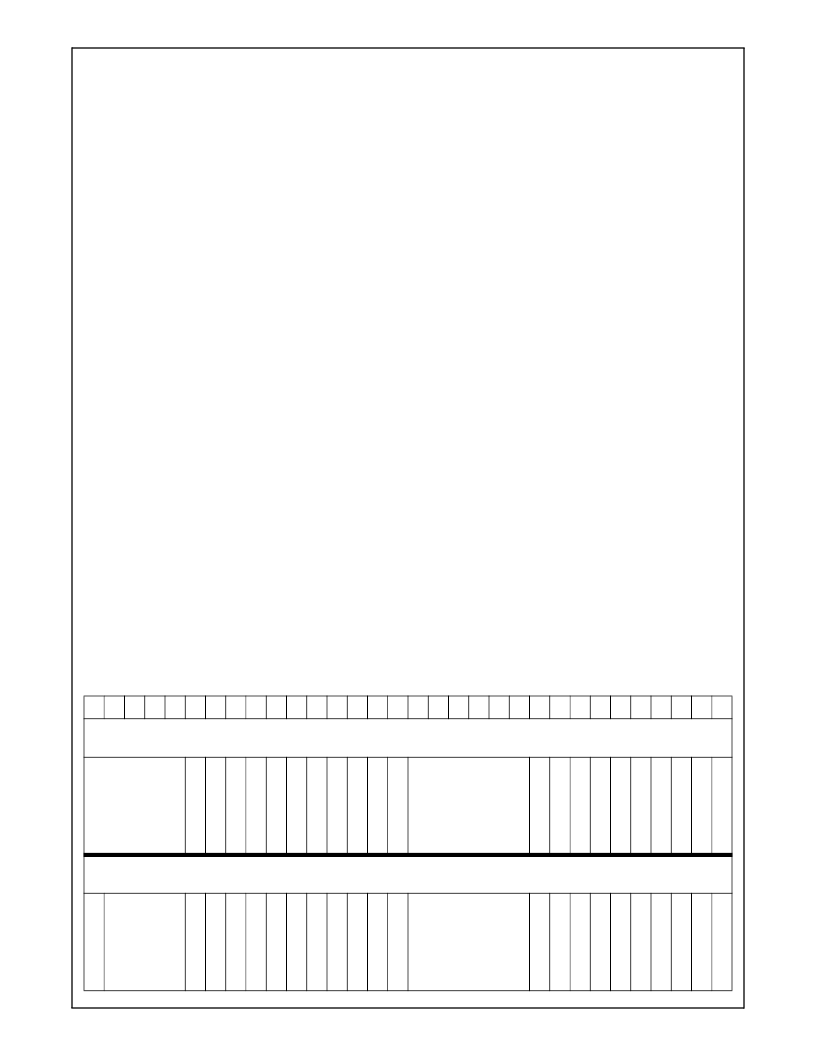

Table 3-3. IntEvent and IntMask Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

BAR0+Offset 80h

BAR0+Offset 84h

IntEvent Set Register

IntEvent Clear Register

RSVD

p

c

u

c

c

c

c

p

R

b

s

RSVD

l

p

i

i

R

R

A

A

r

r

BAR0+Offset 88h

BAR0+Offset 8Ch

IntMask Set Register

IntMask Clear Register

m

RSVD

p

c

u

c

c

c

c

p

R

b

s

RSVD

l

p

i

i

R

R

A

A

r

r

相关PDF资料 |

PDF描述 |

|---|---|

| CS4215-KL | 16-Bit Multimedia Audio Codec |

| CS4215-KQ | 16-Bit Multimedia Audio Codec |

| CS4215 | 16-Bit Multimedia Audio Codec |

| CS4216 | 16-Bit Stereo Audio Codec |

| CS4216-KL | IC EEPROM SRL 256-8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4211-4 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Optoelectronic |

| CS4211-KM | 制造商:CRISTAL 功能描述:4211-KM |

| CS4212-KL | 制造商: 功能描述:4212KL |

| CS4213GP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:摩托车点火器电路 =MB4213 |

| CS4215 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Multimedia Audio Codec |

发布紧急采购,3分钟左右您将得到回复。