- 您现在的位置:买卖IC网 > PDF目录380066 > CS4216-KQ (CIRRUS LOGIC INC) 16-Bit Stereo Audio Codec PDF资料下载

参数资料

| 型号: | CS4216-KQ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Stereo Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封装: | TQFP-44 |

| 文件页数: | 15/58页 |

| 文件大小: | 799K |

| 代理商: | CS4216-KQ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

SERIAL MODE 2, SM2

Serial Mode 2 is enabled by setting SMODE3 =

SMODE2 = 0, and SMODE1 = 1. SM2 is simi-

lar to SM1 except that SCLK is fixed at 256

×

Fs and is the master clock instead of CLKIN.

The CLKIN pin is ignored in this mode and

should be tied low. In SM2, the sample fre-

quency will scale linearly with the frequency of

SCLK. Up to four codecs may occupy the serial

bus since each codec requires only 64 bit periods

and a frame is fixed at 256 bit periods. The se-

rial data format is the same as SM1 and is

illustrated in Figures 5 and 6.

The multifunction pins in SM2 are defined iden-

tically to SM1. See

Serial Mode 1, SM1

section

for more details.

SERIAL MODE 3, SM3

Serial Mode 3 is enabled by setting

SMODE3 = 0, SMODE2 = 1 and SMODE1 = 0.

This mode is designed to interface easily to

DSPs and has the added versatility of a program-

mable number of bits per frame, a master mode,

and one extra bit of D/A attenuation. In SM3,

two of the parallel digital input bits and two of

the parallel digital output bits are available.

Master Clock Frequency

In SM3, the master clock, CLKIN, must be

256

×

Fs

max

. For example, given a 48 kHz maxi-

mum sample frequency, the master clock

frequency must be 12.288 MHz. SCLK and

SSYNC must be synchronous to CLKIN.

D/A Attenuation

SM3 has one more bit per channel allocated for

D/A attenuation which doubles the attenuation

range. Figure 5 illustrates the serial data in,

SDIN, sub-frame for all SM3 sub-modes. The

upper portion of this figure shows modes SM1

and SM2 where the D/A attenuation is located in

Word B, bits 53 through 60. Four bits allow at-

tenuation on each channel from 0 dB down to

-22.5 dB using 1.5 dB steps. In SM3 the attenu-

ation bits are still located in Word B, but start at

bit 51 of the sub-frame. This allows five bits of

attenuation per channel instead of four, produc-

ing an attenuation range for each channel from

0 dB down to -46.5 dB.

In SM3 MF5:DO2 is a general purpose output

and MF6:DI2 is a general purpose input. The

other six multifunction pins are used to select

sub-modes under SM3.

SM3 is divided into two sub-modes, Master and

Slave. In Master sub-mode, the CS4216 gener-

ates SSYNC and SCLK, while in Slave

sub-mode SSYNC and SCLK must be generated

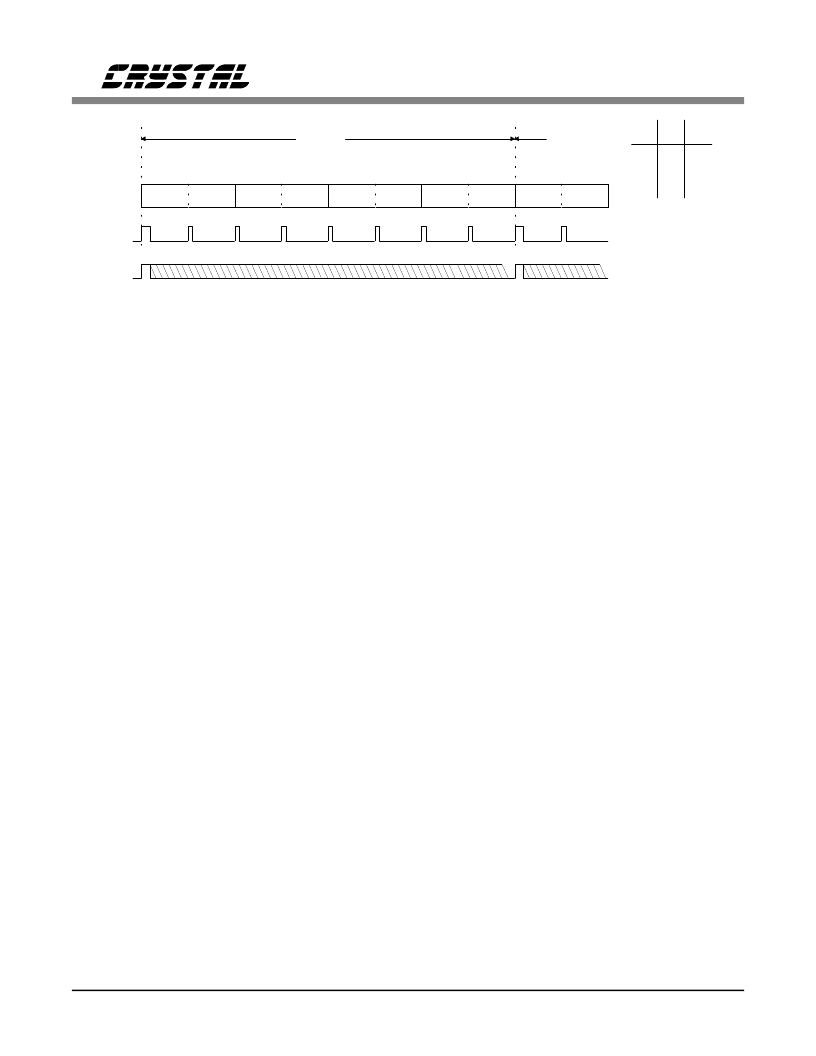

SFS2

SFS1

frame

0

0

1

1

0

1

0

1

1

2

3

4

Sub-frame 1

Sub-frame 2

Sub-frame 3

Sub-frame 4

FRAME (n+1)

Word A

Word B

Word A

Word B

Word A

Word B

Word A

Word B

FRAME n

Sub-frame 1

Word A

Word B

256 SCLK Periods

SSYNC

DATA

FS

WS

WS

WS

WS

WS

WS

WS

FS

WS

FS =

Frame Sync

Low followed by

Two High Bits

WS =

One High

Optional

Not Needed

or

SSYNC

MF8:

MF7:

Sub-

Figure 7. SM1, SM2 - 256 Bits per Frame.

CS4216

DS83F2

15

相关PDF资料 |

PDF描述 |

|---|---|

| CS4218-KL | 16-Bit Stereo Audio Codec |

| CS4218-KQ | 16-Bit Stereo Audio Codec |

| CS4218 | 16-Bit Stereo Audio Codec |

| CS4220 | 24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KS | IC EEPROM SRL 512X8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4220 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit Stereo Audio Codec with 3V Interface |

发布紧急采购,3分钟左右您将得到回复。