- 您现在的位置:买卖IC网 > PDF目录380066 > CS4216-KQ (CIRRUS LOGIC INC) 16-Bit Stereo Audio Codec PDF资料下载

参数资料

| 型号: | CS4216-KQ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Stereo Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封装: | TQFP-44 |

| 文件页数: | 41/58页 |

| 文件大小: | 799K |

| 代理商: | CS4216-KQ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

either serial mode 3, SM3, or serial mode 4,

SM4. Serial modes 1 and 2, SM1 and SM2, are

primarily designed for ASICs and are less flex-

ible. SM1 and SM2 are not available on the

CS4218. The CS4218 has additional SM3 sub-

modes: Multiplier Master (SM3-MM) and

Multiplier Slave (SM3-MS). These sub-modes

are identical to the SM3 Master and Slave sub-

modes except that the master clock, CLKIN,

must be 16xFs

max

instead of 256xFs

max

. The

CS4218 also provides a master I

2

S mode. In

master sub-modes, the CS4216/8 output SSYNC

and SCLK. In slave sub-modes, SSYNC and

SCLK must be externally generated and must be

synchronous to CLKIN.

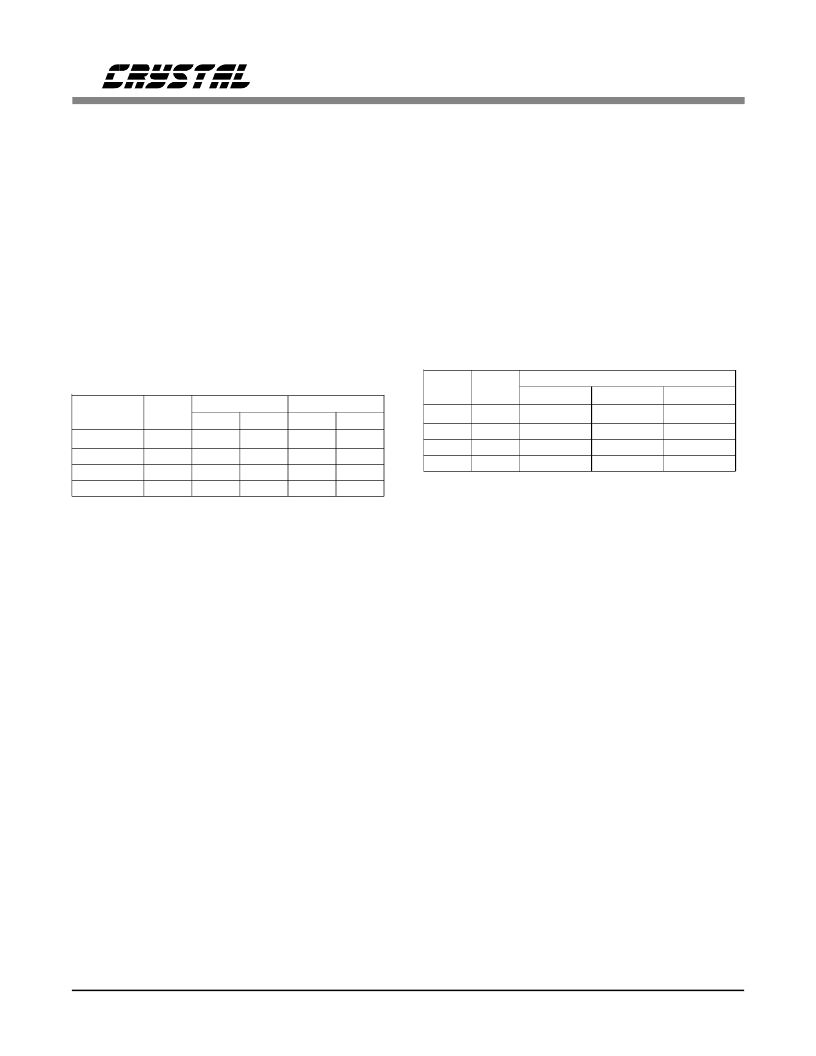

Bits per Frame Selection

The next decision is selecting the number of bits

per frame which defines how many codecs can

sit on the same serial bus. Each codec occupies a

sub-frame and 1 to 4 sub-frames make up a

frame. A sub-frame is 64 bits in SM1, SM2, and

SM3; and 32 bits in SM4. Table 2 lists the possi-

ble selections. If the evaluation board serial port

is shared with other devices, SDOUTUB must be

used instead of SDOUT since SDOUTUB,

driven directly from the chip, must only drive

the time slot assigned to it. See the

Audio Port

Header

section for more information.

Time Slot Selection

If the number of bits per frame selected allows

for more than one codec sub-frame, then the ac-

tual time slot or sub-frame used by the eval

board must be selected. This is done with the

TS2 and TS1 DIP switches. If the number of bits

per frame allows only one codec on the serial

bus, then TS2 and TS1 are ignored. Table 3 list

the decoding for TS2 and TS1. Time slot 1 is the

first sub-frame after SSYNC goes high, time

slot 2 is the next sub-frame, and so on.

Sample Frequency Selection - Master Mode

The last decision is selecting the sample fre-

quency in master sub-mode. If configured for

slave sub-mode, the sample frequency is the ratio

of SCLK to CLKIN as described in the

CS4216/8 Data Sheets. In master modes, three

pins are used to select the sample frequency di-

vide. The DIP switches labeled DIV1, DIV2, and

DIV3 select the sample frequency and are

equivalent to F1, F2, and F3, respectively. The

actual F1-F3 pins on the CS4216/8 are different

between SM3 and SM4 as shown in Table 4 at

the end of the data sheets. Table 3 and Table 9 of

the CS4216 Data Sheet describe the sample fre-

quencies obtained using the on-board oscillator

of 11.2896 MHz. As an example, if all DIV

switches are off, the sample frequency is

44.1 kHz. With only DIV2 on, the sample fre-

quency is 22.05 kHz. To obtain a sample

frequency of 44.1 kHz using the CDB4218, all

DIV switches should be set to zero and a

705.6 kHz clock should be connected to the

BNC jack (J2). The shunt on J1 should be set to

EXT.

BPF

2

0

0

1

1

* SCLK is master clock.

S SM3 SM4

SM2

SL

256

64

256

128

256

256

256

256*

1

0

1

0

1

MA

64

128

128

128

SL

32

64

128

128

MA

32

64

64

64

Table 2. DIP Switch, Bits per Frame

TS2

TS1

Available Sub-frames

4

0

0

1

0

1

2

1

0

3

1

1

4

Table 3. DIP Switch, Time Slots

2

1

2

2

2

1

1

1

1

1

CDB4216

DS83DB4

41

相关PDF资料 |

PDF描述 |

|---|---|

| CS4218-KL | 16-Bit Stereo Audio Codec |

| CS4218-KQ | 16-Bit Stereo Audio Codec |

| CS4218 | 16-Bit Stereo Audio Codec |

| CS4220 | 24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KS | IC EEPROM SRL 512X8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4220 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit Stereo Audio Codec with 3V Interface |

发布紧急采购,3分钟左右您将得到回复。