- 您现在的位置:买卖IC网 > PDF目录380066 > CS4216-KQ (CIRRUS LOGIC INC) 16-Bit Stereo Audio Codec PDF资料下载

参数资料

| 型号: | CS4216-KQ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Stereo Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封装: | TQFP-44 |

| 文件页数: | 18/58页 |

| 文件大小: | 799K |

| 代理商: | CS4216-KQ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

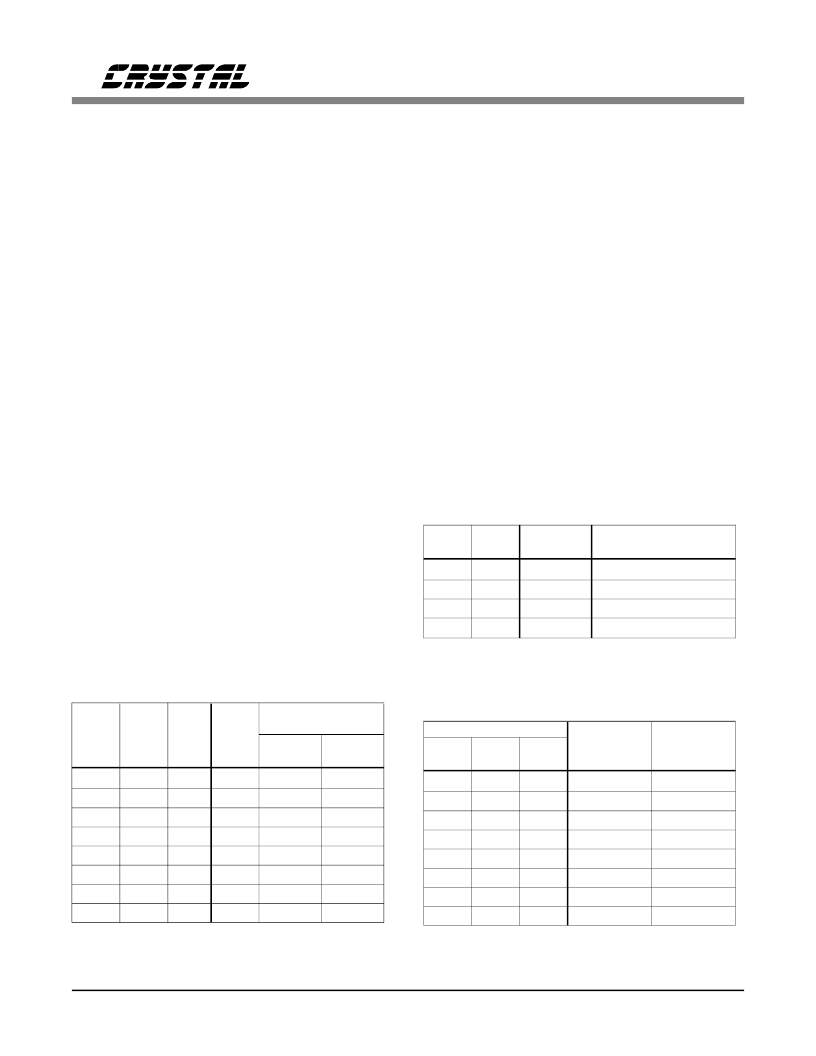

Bits per Frame (Slave Sub-Mode)

In Slave sub-mode, MF1:F1 and MF2:F2 select

the number of bits per frame which determines

how many CS4216’s can occupy one serial port.

Table 4 lists the decoding for MF1:F1 and

MF2:F2.

When set for 64 SCLKs per frame, one device

occupies the entire frame; therefore, a sub-frame

is equivalent to a frame. MF7:SFS1 and

MF8:SFS2 must be set to zero. See Figure 10.

When set for 128 SCLKs per frame, two devices

can occupy the serial port, with MF7:SFS1 se-

lecting the particular sub-frame. MF8:SFS2 must

be set to zero. See Figure 11.

When set for 256 SCLKs per frame (MF1:F1,

MF2:F2 = 10), four devices can occupy the se-

rial port. In this format both MF8:SFS2 and

MF7:SFS1 are used to select the particular sub-

frame. See Figure 12.

In all three of the above Slave sub-mode for-

mats, the frequency of the incoming SCLK

signal, in relation to the master clock provided

on the CLKIN pin, determines the sample fre-

quency. The CS4216 determines the ratio of

SCLK to CLKIN and sets the internal operating

frequency accordingly. Table 5 lists the SCLK to

CLKIN frequency ratio used to determine the

codec’s sample frequency. To obtain a given

sample frequency, SCLK must equal CLKIN di-

vided by the number in the table, based on the

number of bits per frame. As an example, assum-

ing 64 BPF (bits per frame) and

CLKIN = 12.288 MHz, if a sample frequency of

24 kHz is desired, SCLK must equal CLKIN di-

vided by 8 or 1.536 MHz.

When MF1:F1 = MF2:F2 = 1, SCLK is used as

the master clock and is assumed to be 256 times

the sample frequency. In this mode, CLKIN is

ignored and the sample frequency is linearly

scaled with SCLK. (The CLKIN pin must be

tied low.) This mode also fixes SCLK at 256 bits

per frame with MF7:SFS1 and MF8:SFS2 select-

ing the particular sub-frame.

Fs (kHz)

with CLKIN

12.288

MHz

48.00

32.00

24.00

19.20

16.00

12.00

9.60

8.00

MF1:

F1

MF2:

F2

MF3:

F3

N

11.2896

MHz

44.10

29.40

22.05

17.64

14.70

11.025

8.82

7.35

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

256

384

512

640

768

1024

1280

1536

Table 3. SM3-Master, Fs Select

MF1:

F1

0

0

1

1

SCLK is master clock. CLKIN is not used.

MF2:

F2

0

1

0

1

Bits per

Frame

64

128

256

256

Sample Frequency/

SCLK

ratio to CLKIN sensed

ratio to CLKIN sensed

ratio to CLKIN sensed

fixed

. = 256

×

Fs

Table 4. SM3-Slave, Bits per Frame.

SCLK to CLKIN Ratio

BPF

BPF

256

128

1

2

1.5

3

2

4

2.5

5

3

6

4

8

5

10

6

12

Fs (kHz)

with CLKIN with CLKIN

12.288 MHz 11.2896 MHz

48.00

32.00

24.00

19.20

16.00

12.00

9.60

8.00

Fs (kHz)

BPF

64

4

6

8

10

12

16

20

24

44.10

29.40

22.05

17.64

14.70

11.025

8.82

7.35

Table 5. SM3-Slave, Fs Select.

CS4216

18

DS83F2

相关PDF资料 |

PDF描述 |

|---|---|

| CS4218-KL | 16-Bit Stereo Audio Codec |

| CS4218-KQ | 16-Bit Stereo Audio Codec |

| CS4218 | 16-Bit Stereo Audio Codec |

| CS4220 | 24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KS | IC EEPROM SRL 512X8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4220 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit Stereo Audio Codec with 3V Interface |

发布紧急采购,3分钟左右您将得到回复。