参数资料

| 型号: | CS4265-CNZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 20/46页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 24BIT 104DB 32QFN |

| 标准包装: | 60 |

| 类型: | 立体声音频 |

| 数据接口: | PCM 音频接口 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 2 |

| 三角积分调变: | 是 |

| 动态范围,标准 ADC / DAC (db): | 104 / 104 |

| 电压 - 电源,模拟: | 3.13 V ~ 5.25 V |

| 电压 - 电源,数字: | 3.13 V ~ 5.25 V |

| 工作温度: | -10°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-QFN |

| 供应商设备封装: | 32-QFN 裸露焊盘(5x5) |

| 包装: | 托盘 |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 配用: | 598-1001-ND - BOARD EVAL FOR CS4265 CODEC |

| 其它名称: | 598-1039 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

DS657F3

27

CS4265

4.4

Analog Input Multiplexer, PGA, and Mic Gain

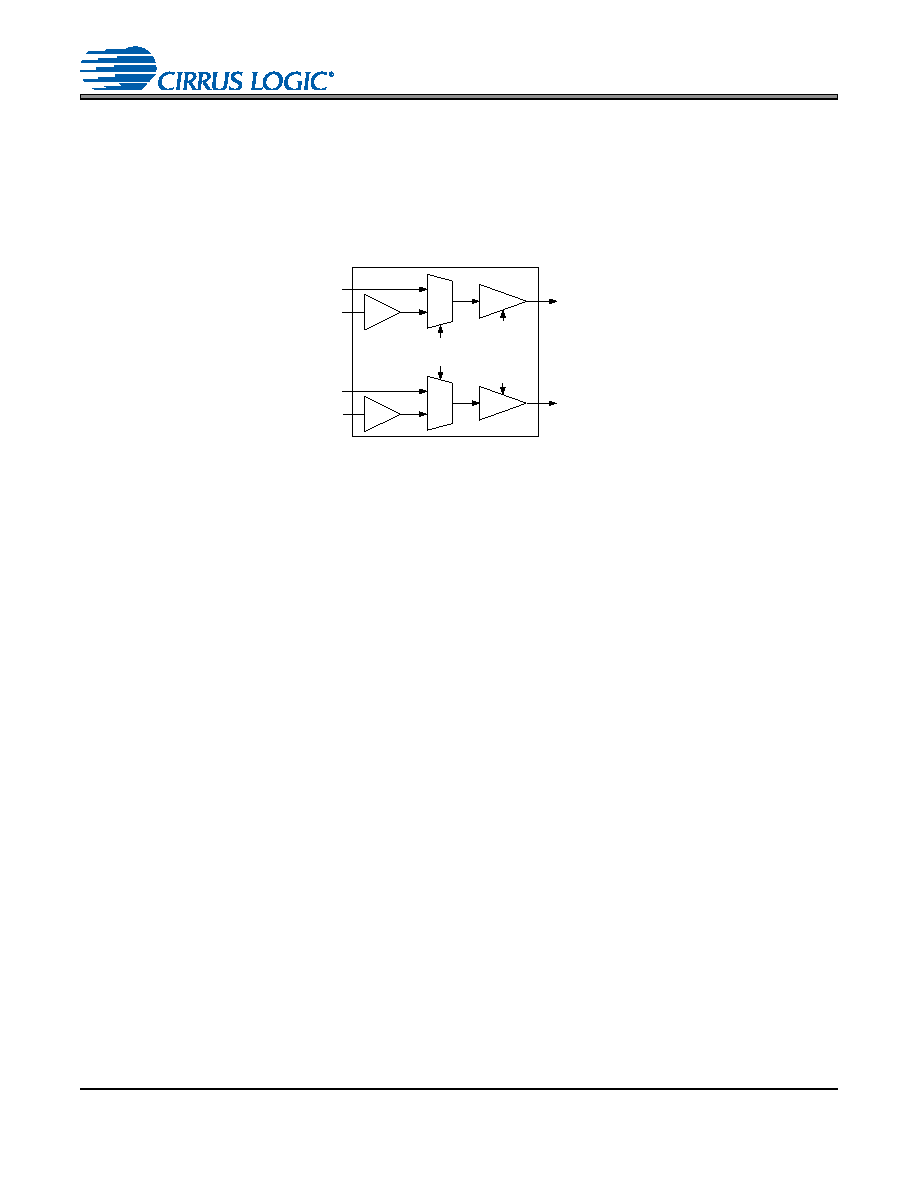

The CS4265 contains a stereo 2-to-1 analog input multiplexer followed by a programmable gain amplifier

(PGA). The input multiplexer is able to select either a line-level input source, or a mic-level input source, and

route it to the PGA. The mic-level input passes through a +32 dB gain stage prior to the input multiplexer,

allowing it to be used for microphone-level signals without the need for any external gain. The PGA stage

provides 12 dB of gain or attenuation in 0.5 dB steps. Figure 11 shows the architecture of the input multi-

plexer, PGA, and mic gain stages.

The “Analog Input Selection (Bit 0)” on page 41 outlines the bit settings necessary to control the input mul-

tiplexer and mic gain. “Channel B PGA Control - Address 07h” on page 40 and “Channel A PGA Control -

Address 08h” on page 40 outline the register settings necessary to control the PGA. By default, the line-

level input is selected by the input multiplexer, and the PGA is set to 0 dB.

4.5

Input Connections

The analog modulator samples the input at 6.144 MHz (MCLK=12.288 MHz). The digital filter will reject sig-

nals within the stopband of the filter. However, there is no rejection for input signals

which are

(n 6.144 MHz) the digital passband frequency, where n=0,1,2,... Refer to the Typical Connection Diagram

for the recommended analog input circuit that will attenuate noise energy at 6.144 MHz. The use of capac-

itors which have a lar ge voltage coefficient (such as ge neral-purpose ceramics) must be avoided since

these can degrade signal linearity. Any unused analog input pairs should be left unconnected.

4.5.1

Pseudo-Differential Input

The CS4265 implements a pseudo-differential input stage. The SGND input is intended to be used as a

pseudo-differential reference signal. This feature allows for common mode noise rejection with single-

ended signals. Figure 12 shows a basic diagram outlining the internal implementation of the pseudo-dif-

ferential input stage. The Typical Connection Diagram shows the recommended pseudo-differential input

PGA

MUX

+32 dB

AINA

MICIN1

Channel B

PGA Gain Bits

Out to ADC

Channel A

Out to ADC

Channel B

MUX

+32 dB

AINB

MICIN2

PGA

Analog Input

Selection Bits

Channel A

PGA Gain Bits

Figure 11. Analog Input Architecture

相关PDF资料 |

PDF描述 |

|---|---|

| CS4270-DZZ | IC CODEC 24BIT 105DB 24TSSOP |

| CS4271-DZZ | IC CODEC 24BIT 114DB 28-TSSOP |

| CS4272-DZZ | IC CODEC 24BIT 114DB 28-TSSOP |

| CS4299-JQZR | IC CODEC AC 97 W/SRC 48-LQFP |

| CS42L51-DNZ | IC CODEC STEREO W/HDPN AMP 32QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4265-CNZ/C1 | 制造商:Cirrus Logic 功能描述: |

| CS4265-CNZR | 功能描述:接口—CODEC IC 24bit 192kHz Str Cdc w/PGA &Inpt Mux RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4265-DNZ | 功能描述:接口—CODEC Stereo Audio CODEC 104 dB 192 kHz RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4265-DNZR | 功能描述:接口—CODEC IC 24-bit 192kHz Str Cdc w/PGA &Inpt Mux RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4267AM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。