- 您现在的位置:买卖IC网 > PDF目录10545 > CS5513-BSZ (Cirrus Logic Inc)IC ADC 20BIT INTERNAL OSC 8SOIC PDF资料下载

参数资料

| 型号: | CS5513-BSZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 8/26页 |

| 文件大小: | 0K |

| 描述: | IC ADC 20BIT INTERNAL OSC 8SOIC |

| 标准包装: | 100 |

| 位数: | 20 |

| 采样率(每秒): | 326 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.7mW |

| 电压电源: | 双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

| 输入数目和类型: | 1 个差分,双极 |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 其它名称: | 598-1707 |

CS5510/11/12/13

16

DS337F4

2.5.1

Reading Conversions -

CS5510/12

After power-up, the CS5510/12 will begin convert-

ing once a clock source is applied to the SCLK pin.

When a conversion has completed, and there is

new data in the output register, the SDO line will

fall to a logic-low level if CS is also at a logic-low

state (SDO will always be high-impedance when

CS is high). If CS is low at the end of the conver-

sion cycle, SDO will fall on the rising edge of an

SCLK. After SCLK falls, the next SCLK cycle (high,

then low) will begin clocking out the data. The first

data bit therefore, is 1-

SCLK cycles wide. Twen-

ty-four SCLK cycles (after the initial high-low tran-

sition) are needed to retrieve the conversion word

bits can be read on the rising edge of SCLK, and

the next data bit is output to SDO on the falling

edge of SCLK. Once the entire data word has been

read, SDO will return to a logic-high state until

there is a new conversion word available. If CS is

at a logic-high at the end of the conversion cycle,

the data will not be shifted out of the part until CS

is brought to a logic-low state during the next con-

version cycle. If a new conversion becomes avail-

able while the current data is being read, the data

register will not be updated, and the new conver-

sion word will be lost. The user need not read every

conversion. If the user chooses not to read a con-

version, CS should remain at a logic-high state for

the duration of the conversion cycle. Note that if

CS goes to a logic-high state during a read, the

current conversion data will be lost and replaced

by a new conversion word when the new conver-

sion data is available.

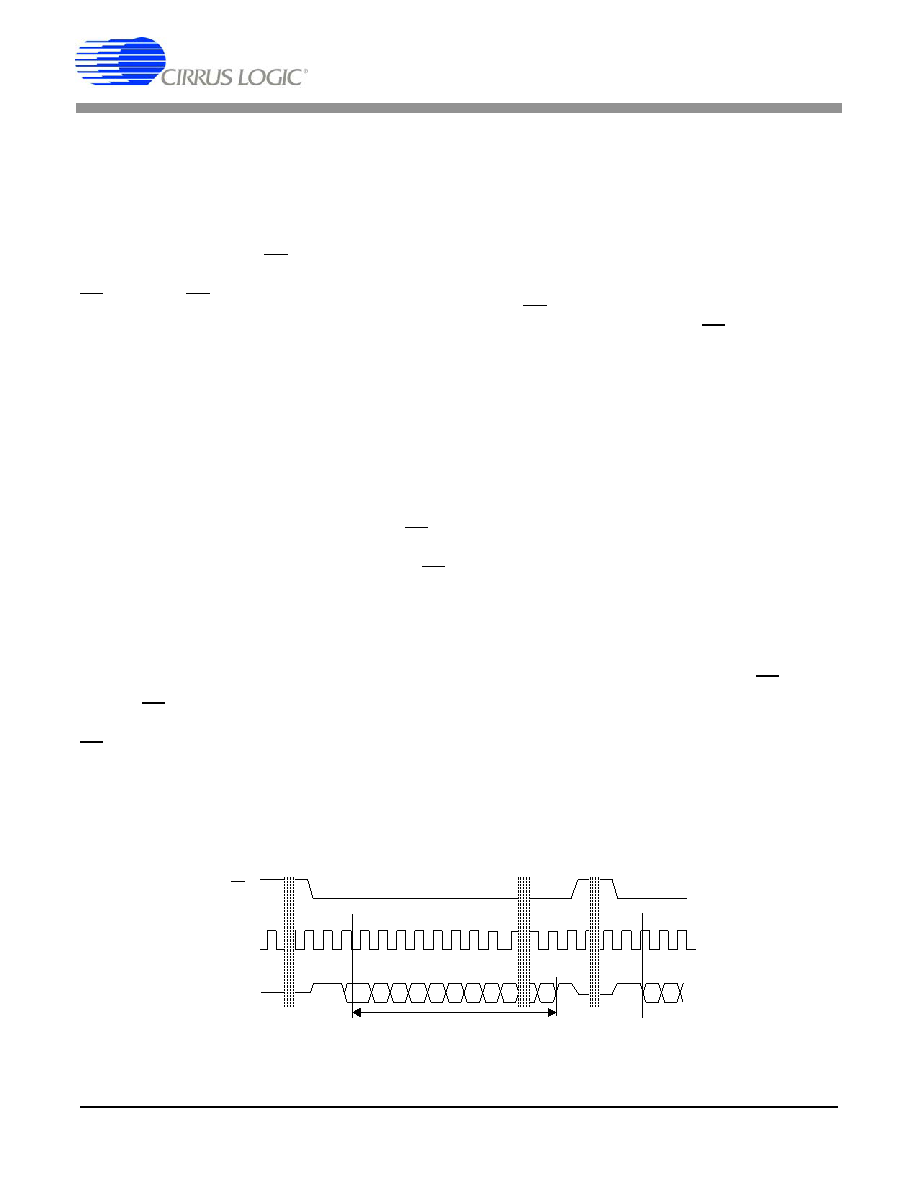

2.5.2

Reading Conversions -

CS5511/13

After power-up, the CS5511/13 begins converting

and updating the output register. When there is

new data in the output register (at the end of a con-

version cycle) the SDO line will fall to a logic-low

level if CS is also at a logic-low state (SDO will al-

ways be high-impedance when CS is high). Twen-

ty-four SCLK cycles are needed to retrieve the

conversion word from the device (see Figures 18

and 19). The data bits can be read on the rising

edge of SCLK, and the next data bit is output to

SDO on the falling edge of SCLK. Once the entire

data word has been read, SDO will return to a log-

ic-high state until there is a new conversion word

available. If new conversions become available

while the current data is being read, the data regis-

ter will not be updated, and the new conversions

will be lost. The user need not read every conver-

sion. If the user chooses not to read a conversion

after SDO falls, SDO will rise seventeen oscillator

clock cycles (of the internal oscillator) before the

next conversion word is available and then fall

again to signal that the conversion is complete.

Note that if a conversion word is not read before

the next conversion word is ready, or if CS goes to

a logic-high state during a read, the current conver-

sion data will be lost and replaced by a new con-

version word when the new conversion data is

available.

SD O

SC L K

Da ta T im e

24 S C LK s

MS B

LSB

CS

0

OF

OD

0

00

0

Figure 16. Data Word Timing for the CS5510.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BTR-MX-F1 | CONVERTER MOD DC/DC 7.5V 75W |

| VI-JVP-MY-F2 | CONVERTER MOD DC/DC 13.8V 50W |

| VE-BTR-MW | CONVERTER MOD DC/DC 7.5V 100W |

| 97-3108B-16S-1S | CONN PLUG 7POS RT ANG W/SKT |

| VI-JVN-MY-F1 | CONVERTER MOD DC/DC 18.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5513-BSZR | 功能描述:模数转换器 - ADC IC 20-Bit 8-Pin Delta Sigma ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5516 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16BIT/20-BIT BRIDGE TRANSDUCER A/D CONVERTER |

| CS5516-AP | 功能描述:模数转换器 - ADC 16-Bit Bridge Transducer ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5516-APZ | 制造商:Cirrus Logic 功能描述: |

| CS5516-AS | 功能描述:模数转换器 - ADC 16-Bit Bridge Transducer ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。