参数资料

| 型号: | CS8406-DZZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 15/28页 |

| 文件大小: | 0K |

| 描述: | IC XMITTER DGTL 192KHZ 28TSSOP |

| 标准包装: | 50 |

| 类型: | 数字音频接口发射器 |

| 应用: | 车载音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 配用: | 598-1017-ND - BOARD EVAL FOR CS8416 RCVR |

| 其它名称: | 598-1722 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

22

DS580F6

CS8406

8.7

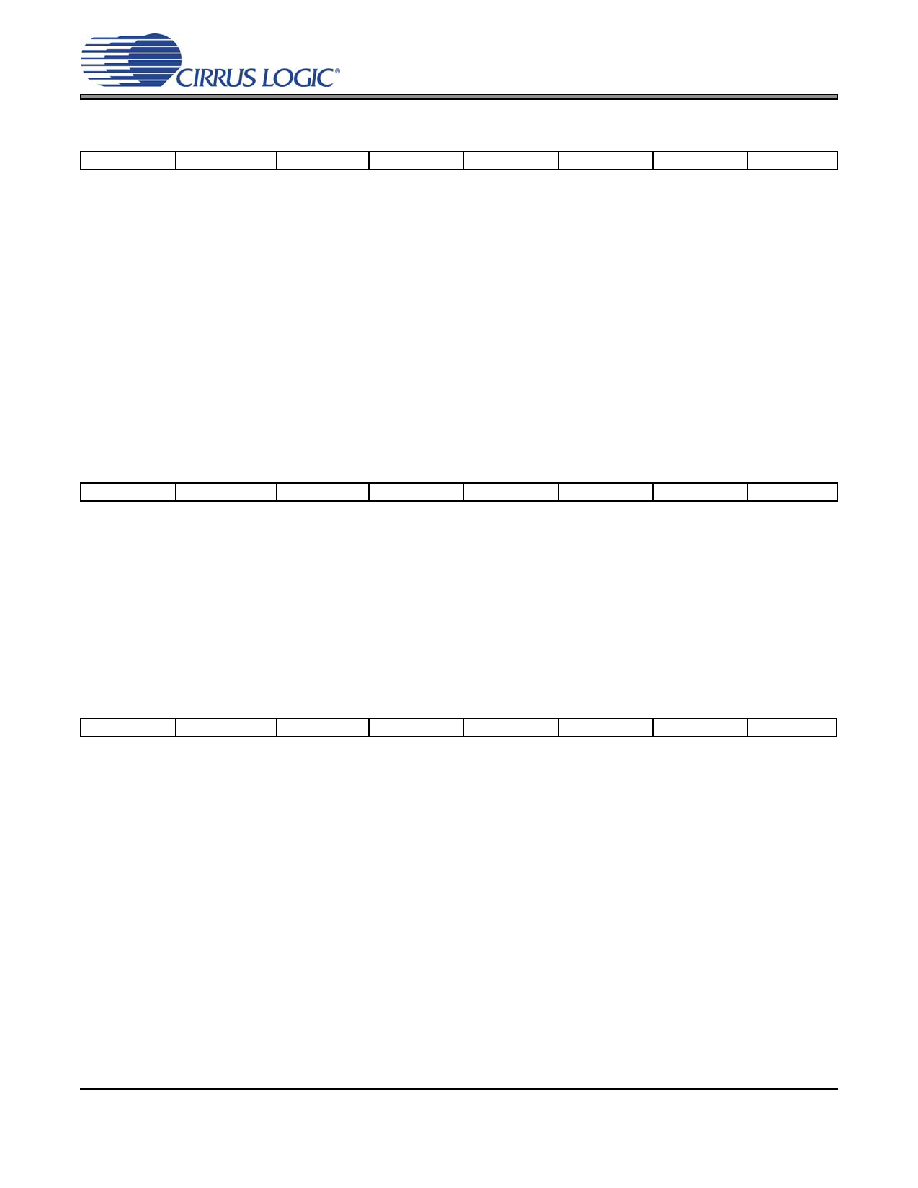

Interrupt 1 Status (07h) (Read Only)

For all bits in this register, a ‘1’ means the associated interrupt condition has occurred at least once since

the register was last read. A ‘0’ me ans the associated interrupt condition has NOT occurred since the last

reading of the register. Reading the register resets all bits to ‘0’, unless the Interrupt Mode is set to level and

the interrupt source is still true. Status bits that are masked off in the associated mask register will always

be ‘0’ in this register. This register defaults to 00h.

TSLIP - AES3 transmitter source data slip interrupt

In data flows where OMCK, which clocks the AES3 transmitter, is asynchronous to the data source, this bit

will go high every time a data sample is dropped or repeated. When TCBL is an input, this bit will go high

on receipt of a new TCBL signal.

EFTC - E to F C-buffer transfer interrupt. The source for this bit is true during the E to F buffer transfer in

the C bit buffer management process.

8.8

Interrupt 2 Status (08h) (Read Only)

For all bits in this register, a ‘1’ means the associated interrupt condition has occurred at least once since

the register was last read. A ‘0’ me ans the associated interrupt condition has NOT occurred since the last

reading of the register. Reading the register resets all bits to ‘0’, unless the Interrupt Mode is set to level and

the interrupt source is still true. Status bits that are masked off in the associated mask register will always

be ‘0’ in this register. This register defaults to 00h.

EFTU - E to F U-buffer transfer interrupt. (Block Mode only) The source of this bit is true during the E to F

buffer transfer in the U bit buffer management process.

8.9

Interrupt 1 Mask (09h)

The bits of this register serve as a mask for the Interrupt 1 register. If a mask bit is set to 1, the error is un-

masked, meaning that its occurrence will affect the INT pin and the status register. If a mask bit is set to 0,

the error is mas ked, meaning that its occurrence will not affect the INT pin or the status register. The bit

positions align with the corresponding bits in Interrupt 1 register. This register defaults to 00h.

7

6

5

432

1

0

TSLIP

0

EFTC

0

7

6

5

432

1

0

00

0

EFTU

0

7

6

5

432

1

0

TSLIPM

0

EFTCM

0

相关PDF资料 |

PDF描述 |

|---|---|

| CS8415A-CZZ | IC 96KHZ DGTL RCVR 28-TSSOP |

| CS8416-DZZ | IC RCVR DGTL 192KHZ 28TSSOP AUTO |

| CS8420-DSZ | IC CONV S/R DGTL AUDIO 28-SOIC |

| CS8421-CNZ | IC SAMPLE RATE CONVERTER 20QFN |

| CS8427-DZZ | IC TXRX DGTL AUDIO 96KHZ 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS8406-DZZR | 功能描述:音频发送器、接收器、收发器 IC 192 kHz Digital Audio Transmitter RoHS:否 制造商:Cirrus Logic 工作电源电压:3.3 V, 5 V 电源电流:11.8 mA 通道数量:1 最大工作温度:+ 70 C 接口类型:I2C, SPI 安装风格:SMD/SMT 封装 / 箱体:TSSOP-28 封装: |

| CS8406-IS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS8406-IZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS841 | 制造商:HVPSI 制造商全称:High Voltage Power Solutions, Inc. 功能描述:MOV Modules |

| CS8411 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:DIGITAL AUDIO INTER FACE RECEIVER |

发布紧急采购,3分钟左右您将得到回复。