- 您现在的位置:买卖IC网 > PDF目录298975 > CY3764VP208-200UXC (Cypress Semiconductor Corp.) BATT SEALED LEAD ACID 12V 2.3AH PDF资料下载

参数资料

| 型号: | CY3764VP208-200UXC |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | BATT SEALED LEAD ACID 12V 2.3AH |

| 中文描述: | 为5V,3.3V,ISRTM高性能的CPLD |

| 文件页数: | 10/64页 |

| 文件大小: | 1798K |

| 代理商: | CY3764VP208-200UXC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Ultra37000 CPLD Family

Document #: 38-03007 Rev. *D

Page 18 of 64

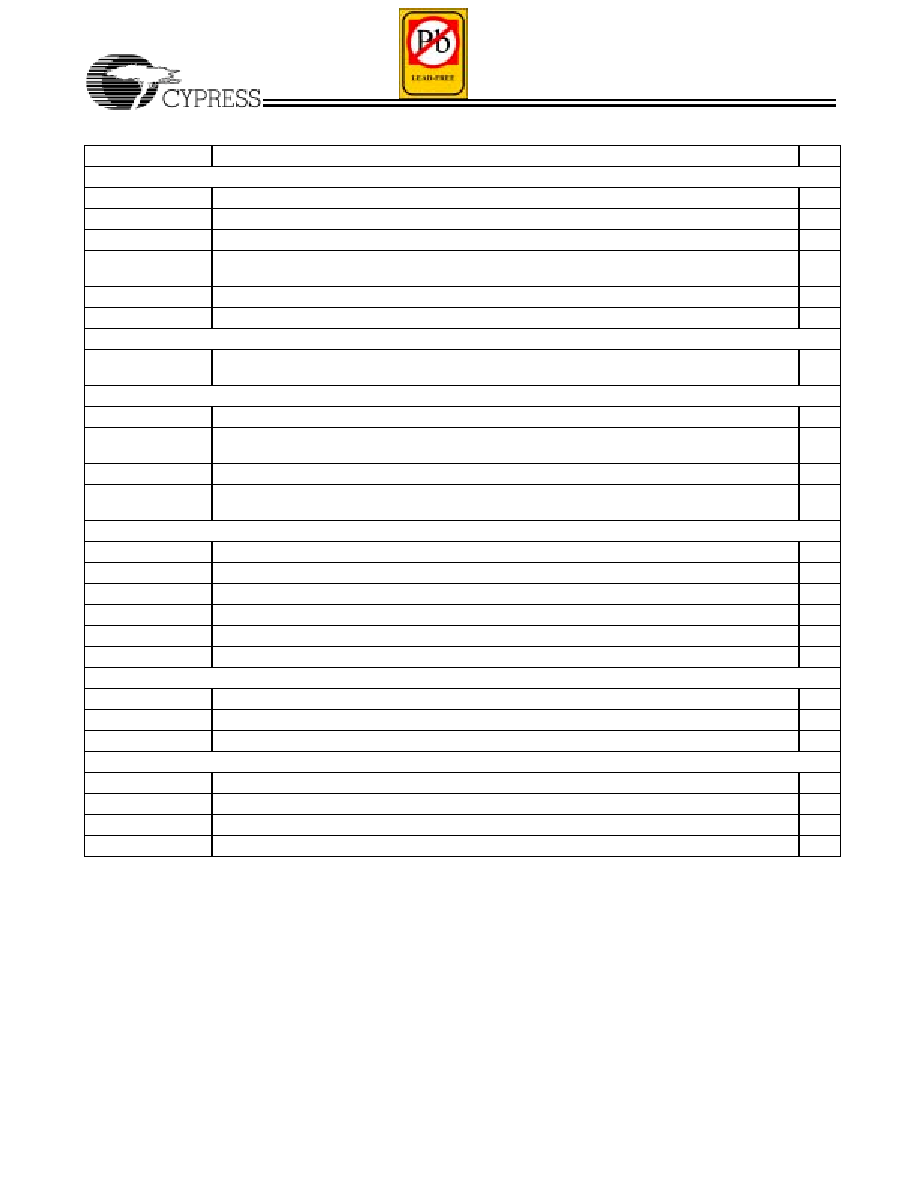

Product Term Clocking Parameters

tCOPT

Product Term Clock or Latch Enable (PTCLK) to Output

ns

tSPT

Set-Up Time from Input to Product Term Clock or Latch Enable (PTCLK)

ns

tHPT

Register or Latch Data Hold Time

ns

tISPT

Set-Up Time for Buried Register used as an Input Register from Input to Product Term Clock or

Latch Enable (PTCLK)

ns

tIHPT

Buried Register Used as an Input Register or Latch Data Hold Time

ns

tCO2PT

Product Term Clock or Latch Enable (PTCLK) to Output Delay (Through Logic Array)

ns

Pipelined Mode Parameters

tICS

Input Register Synchronous Clock (CLK0, CLK1, CLK2, or CLK3) to Output Register Synchronous

Clock (CLK0, CLK1, CLK2, or CLK3)

ns

Operating Frequency Parameters

fMAX1

Maximum Frequency with Internal Feedback (Lesser of 1/tSCS, 1/(tS + tH), or 1/tCO)

MHz

fMAX2

Maximum Frequency Data Path in Output Registered/Latched Mode (Lesser of 1/(tWL + tWH),

1/(tS +tH), or 1/tCO)

MHz

fMAX3

Maximum Frequency with External Feedback (Lesser of 1/(tCO + tS) or 1/(tWL + tWH)

MHz

fMAX4

Maximum Frequency in Pipelined Mode (Lesser of 1/(tCO + tIS), 1/tICS, 1/(tWL + tWH), 1/(tIS + tIH),

or 1/tSCS)

MHz

Reset/Preset Parameters

tRW

Asynchronous Reset Width[5]

ns

tRR

Asynchronous Reset Recovery Time[5]

ns

tRO

Asynchronous Reset to Output

ns

tPW

Asynchronous Preset Width[5]

ns

tPR

Asynchronous Preset Recovery Time[5]

ns

tPO

Asynchronous Preset to Output

ns

User Option Parameters

tLP

Low Power Adder

ns

tSLEW

Slow Output Slew Rate Adder

ns

t3.3IO

3.3V I/O Mode Timing Adder[5]

ns

JTAG Timing Parameters

tS JTAG

Set-up Time from TDI and TMS to TCK[5]

ns

tH JTAG

Hold Time on TDI and TMS[5]

ns

tCO JTAG

Falling Edge of TCK to TDO[5]

ns

fJTAG

Maximum JTAG Tap Controller Frequency[5]

ns

Switching Characteristics Over the Operating Range (continued)[12]

Parameter

Description

Unit

相关PDF资料 |

PDF描述 |

|---|---|

| CY3930V484-125BBC | CPLDs at FPGA Densities |

| CY3950V484-125BBC | CPLDs at FPGA Densities |

| CY54FCT540CTDMB | FCT SERIES, 8-BIT DRIVER, INVERTED OUTPUT, CDIP20 |

| CY54FCT543CTDMB | FCT SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

| CY54FCT543ATDMB | FCT SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。