- 您现在的位置:买卖IC网 > PDF目录170654 > DAC1221EG4 (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 1800 us SETTLING TIME, 16-BIT DAC, PDSO16 PDF资料下载

参数资料

| 型号: | DAC1221EG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 1800 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| 封装: | GREEN, SSOP-16 |

| 文件页数: | 3/16页 |

| 文件大小: | 154K |

| 代理商: | DAC1221EG4 |

11

DAC1221

t

1

t

3

t

4

t

2

t

2

SCLK

Reset On

Falling Edge

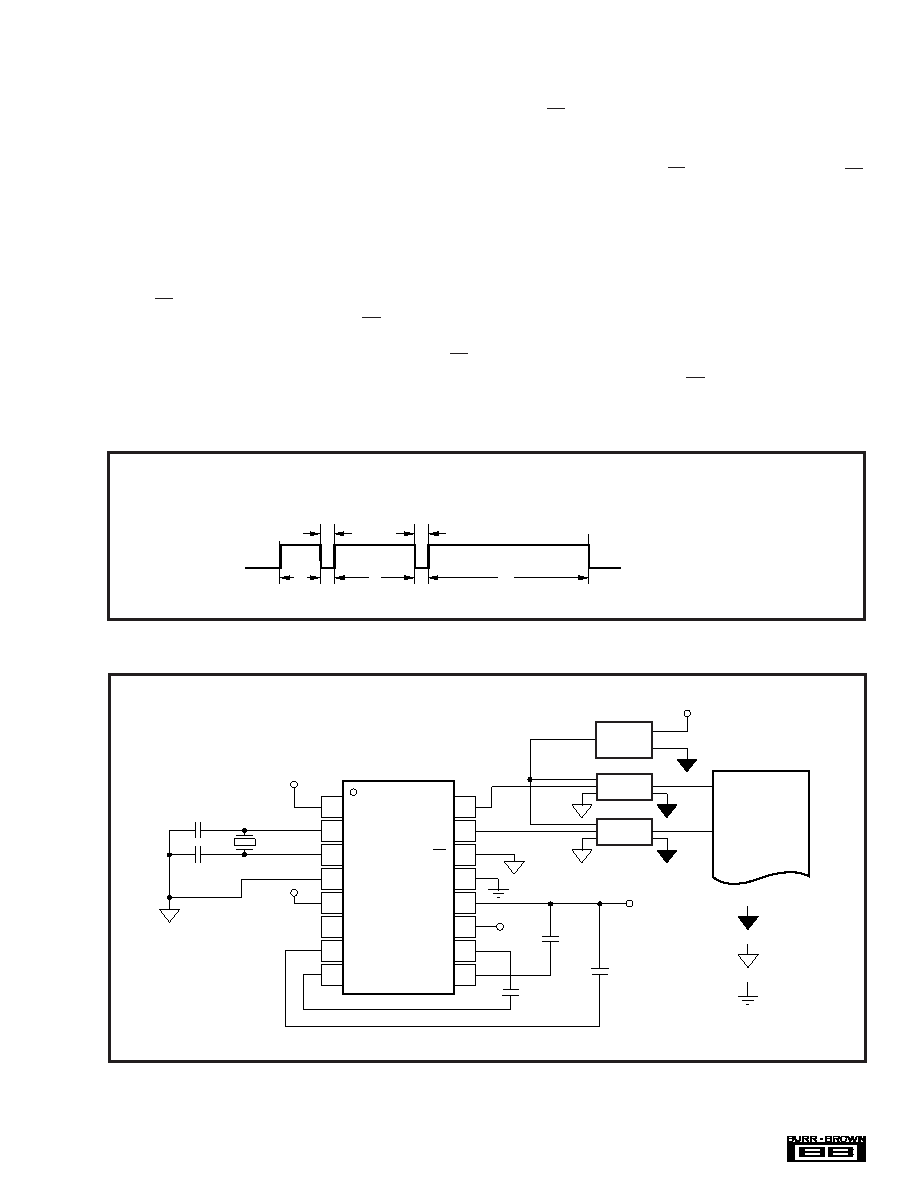

FIGURE 3. Resetting the DAC1221.

t1: > 512 tXIN

< 800 tXIN

t2: > 10 tXIN

t3: > 1024 tXIN

< 1800 tXIN

t4: ≥ 2048 tXIN

< 2400 tXIN

I/O Recovery

If serial communication stops during an instruction or data

transfer for longer than 100ms (for fXIN = 2.5MHz), the

DAC1221 will reset its serial interface. This will not affect

the internal registers. The main controller must not continue

the transfer after this event, but must restart the transfer from

the beginning. This feature is very useful if the main control-

ler can be reset at any point. After reset, simply wait 200ms

(for fXIN = 2.5MHz) before starting serial communication.

Isolation

The serial interface of the DAC1221 provides for simple

isolation methods. An example of an isolated two-wire

interface is shown in Figure 4.

Using CS

The serial interface may make use of the CS signal, or this

input may simply be tied LOW. There are several issues

associated with choosing to do one or the other. The CS

signal does not directly control the tri-state condition of the

SDIO output. These signals are normally in the tri-state

condition. They only become active when serial data is

being transmitted from the DAC1221. If the DAC1221 is in

the middle of a serial transfer and the SDIO is an output,

taking CS HIGH will not tri-state the output signal.

If there are multiple serial peripherals utilizing the same

serial I/O lines and communication may occur with any

peripheral at any time, the CS signal must be used. The CS

signal is then used to enable communication with the

DAC1221.

TIMING

The maximum serial clock frequency cannot exceed the

DAC1221 XIN frequency divided by 10. Table VIII and

Figures 5 through 9 define the basic digital timing character-

istics of the DAC1221. Figure 5 and the associated timing

symbols apply to the XIN input signal. Figures 6 through 9

and associated timing symbols apply to the serial interface

signals (SCLK, SDIO, and CS). The serial interface is

discussed in detail in the Serial Interface section.

1

2

3

4

5

6

7

8

DV

DD

X

OUT

X

IN

DGND

AV

DD

DNC

C

3

C

2B

SCLK

SDIO

CS

AGND

V

REF

V

OUT

C

2A

C

1

16

15

14

13

12

11

10

9

DAC1221

C

1X

5.6pF

C

2X

5.6pF

AV

DD

XTAL

V

REF

DV

DD

P1.1

P1.0

8051

Opto

Coupler

Opto

Coupler

Isolated

Power

C

2

C

3

C

1

= DGND

= AGND

= Isolated

FIGURE 4. Isolation for Two-Wire Interface.

相关PDF资料 |

PDF描述 |

|---|---|

| DAC5311IDCKR | SERIAL INPUT LOADING, 12 us SETTLING TIME, 8-BIT DAC, PDSO6 |

| DAC5311IDCKRG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 8-BIT DAC, PDSO6 |

| DAC5311IDCKTG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 8-BIT DAC, PDSO6 |

| DAC5652AIPFBRG4 | DUAL, PARALLEL, WORD INPUT LOADING, 0.02 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| DAC5672AIPFBRG4 | DUAL, PARALLEL, WORD INPUT LOADING, 0.02 us SETTLING TIME, 14-BIT DAC, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC1221LCN | 制造商:n/a 功能描述:1221 |

| DAC1221LCN/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:12-Bit Digital-to-Analog Converter |

| DAC1221LCN/B+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:12-Bit Digital-to-Analog Converter |

| DAC1222 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:10-Bit, 12-Bit Binary Multiplying D/A Converter |

| DAC1222LCJ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。