- 您现在的位置:买卖IC网 > PDF目录17091 > DAC5674EVM (Texas Instruments)EVAL MODULE FOR DAC5674 PDF资料下载

参数资料

| 型号: | DAC5674EVM |

| 厂商: | Texas Instruments |

| 文件页数: | 25/39页 |

| 文件大小: | 0K |

| 描述: | EVAL MODULE FOR DAC5674 |

| 产品培训模块: | Data Converter Basics |

| 标准包装: | 1 |

| 系列: | CommsDAC™ |

| DAC 的数量: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 400M |

| 数据接口: | 并联 |

| 设置时间: | 20ns |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | DAC5674 |

| 相关产品: | DAC5674IPHPRG4-ND - IC DAC 14BIT 400MSPS 48-HTQFP DAC5674IPHPR-ND - IC DAC 14BIT 400MSPS 48-HTQFP DAC5674IPHPG4-ND - IC DAC 14BIT 400MSPS 48-HTQFP 296-15726-ND - IC DAC 14BIT 400MSPS 48-HTQFP |

| 其它名称: | 296-30860 DAC5674EVM-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

DAC5674

SLWS148A SEPTEMBER 2003 REVISED OCTOBER 2005

www.ti.com

31

The external loop filter components C1, C2, and R1 are given by choosing Gvco, N = Fvco/Fdata, the loop

phase margin

φd and the loop bandwidth ωd. Except for applications where abrupt clock frequency changes

require a fast PLL lock time, it is suggested that

φd be set to at least 80 degrees for stable locking and

suppression of the phase noise side lobes. Phase margins of 60 degrees or less have occasionally been

sensitive to board layout and decoupling details.

The optimum loop bandwidth

ωd depends on both the VCO phase noise, which is largely a function of Gvco,

and the application. For the foregoing example with Gvco = 210 MHz/V, an

ωd = 1 MHz would be typical, but

lower and higher loop bandwidths may provide better phase-noise characteristics. For a higher Gvco, for

example Gvco = 400 MHz/V, a

ωd ≈ 7 MHz would be typical. However, it is suggested that the customer

experiment with varying the loop bandwidth by at least 1/2

× through 2× to verify the optimum setting.

C1, C2, and R1 are then calculated by the following equations:

C1

+ t1 1– t2

t3

C2

+ t1–t2

t3

R1

+

t32

t1(t3 * t2)

where

t1 +

K

dKvco

w2

d

tan

f

d ) secfd

t2 +

1

w

d tan fd ) secfd

t3 +

tan

f

d ) secfd

w

d

and

charge pump current

:

iqp = 1 mA

vco gain:

Kvco = 2

π × Gvco rad/V

Fvco/Fdata:

N = {2, 4, 8, 16, 32}

phase detector gain:

Kd = iqp

× (2πN)1 A/rad

An Excel

spreadsheet is provided by TI for automatically calculating the values for C1, C2, and R.

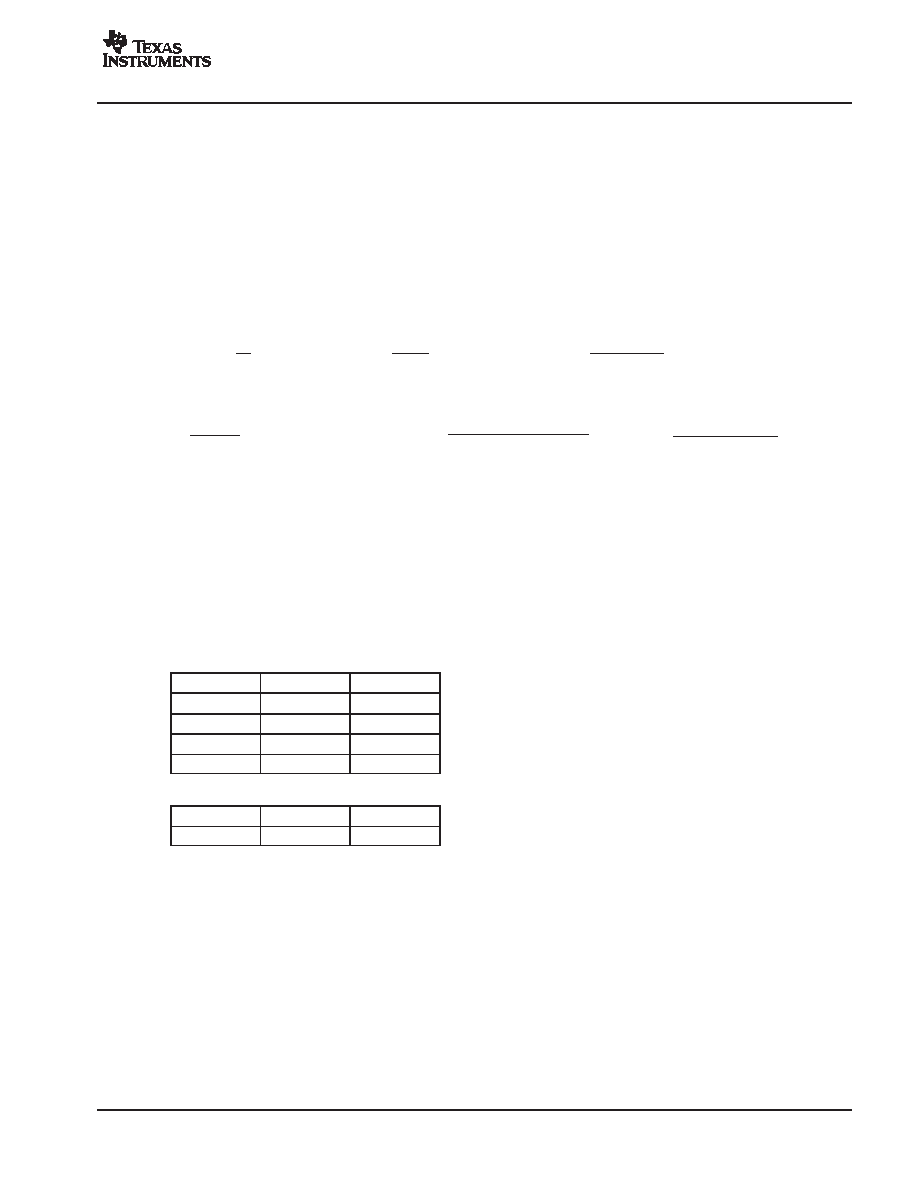

Completing the preceding example with

PARAMETER

VALUE

UNIT

Gvco

2.10E+02

MHz/V

ωd

1.00E+00

MHz

N

4

φd

80

degrees

the component values are

C1 (F)

C2 (F)

R (

W)

1.51E08

1.16E10

1.21E+02

As the PLL characteristics are not sensitive to these components, the closest 20% tolerance capacitor and 1%

tolerance resistor values can be used. If the calculation results in a negative value for C2 or an unrealistically

large value for C1, then the phase margin may need to be reduced slightly.

USING PowerPAD DEVICES

A thermal land should be placed on the top and bottom layers of the circuit board. The recommended thermal

land size for this package is 5 mm

× 5 mm, with top and bottom layers connected by 9 vias. A thermal land size

of 3,8 mm

× 3,8 mm (as used on the DAC5674 EVM) is adequate for this device.

相关PDF资料 |

PDF描述 |

|---|---|

| ELJ-PE5N6KF | INDUCTOR 5.6NH 10% 0603 SMD |

| ECM15DSEN-S13 | CONN EDGECARD 30POS .156 EXTEND |

| AP2280-1FMG-7 | IC LOAD SW CTRL 1CH 6-DFN |

| SDR-X | SCOTCH CODE REFILL X |

| ECM15DSEH-S13 | CONN EDGECARD 30POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5674IPHP | 功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5674IPHPG4 | 功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5674IPHP-ND | 制造商: 功能描述: 制造商:undefined 功能描述: |

| DAC5674IPHPR | 功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5674IPHPRG4 | 功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。