- 您现在的位置:买卖IC网 > PDF目录171212 > DP83957 PDF资料下载

参数资料

| 型号: | DP83957 |

| 文件页数: | 11/24页 |

| 文件大小: | 240K |

| 代理商: | DP83957 |

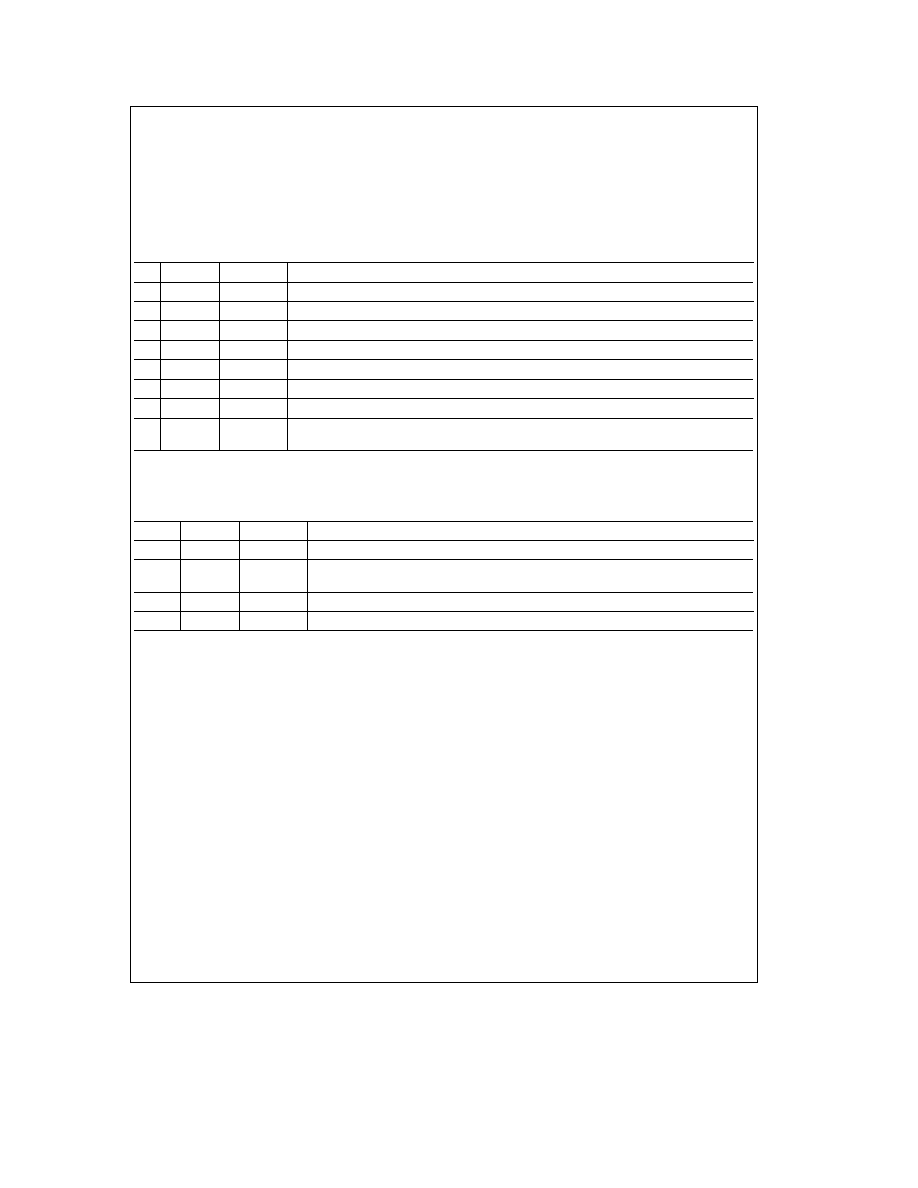

60 Register Description (Continued)

616 PORT ATTRIBUTE STATUS REGISTER 1

The Port Attribute Status Registers 1 and 2 are located in the Port Attribute memory map of each port Port Attribute Registers 1

and 2 are used to indicate if any attributes have changed since the last CPU access to a particular port These registers

therefore provide a status indication of any attribute changes

The CPU needs to ensure that the port Attributes are cleared after a CPU read to these two registers This will guarantee that

the CPU has taken a snap-shot of the Port Attributes correctly The Management block of the DP83957 automatically updates

the attributes on a port-per-packet basis

Reset State

Undefined (SRAM)

Bit

Bit Name

Access

Bit Description

D7

LEVNT

ReadWrite

This status bit indicates whether a port experienced a Late Event

D6

COL

ReadWrite

This status bit indicates whether a port experienced a Collision

D5

RUNT

ReadWrite

This status bit indicates whether a port experienced a Runt

D4

SEVNT

ReadWrite

This status bit indicates whether a port experienced a Short Event

D3

FTL

ReadWrite

This status bit indicates whether a port experienced a Frame Too Long condition

D2

AERR

ReadWrite

This status bit indicates whether a port experienced an Alignment Error

D1

FCSERR

ReadWrite

This status bit indicates whether a port experienced a Frame Check Sequence Error on a packet

D0

RFO

ReadWrite

This status bit indicates whether a port experienced a Readable Frame or a frame with Readable

Octets

617 PORT ATTRIBUTE STATUS REGISTER 2

Port Attribute Status Register 2 is an extension to the Port Attribute Status Register 1 for any port

Reset State

Undefined (SRAM)

Bit

Bit Name

Access

Bit Description

D7 – D3

RES

Reserved

D2

SAC

ReadWrite

This status bit indicates whether a port experienced a change of Source Address from the

address stored in the aLastSourceAddress attribute

D1

DRM

ReadWrite

This status bit indicates whether the port experienced a Data Rate Mismatch

D0

VLE

ReadWrite

This status bit indicates whether the port experienced a Very Long Event

19

相关PDF资料 |

PDF描述 |

|---|---|

| DP83957VF | REPEATER MANAGEMENT|QFP|80PIN|PLASTIC |

| DP83959AVUL | LAN Hub Controller |

| DP83BC04BJ | Single 8-bit Bus Transceiver |

| DP83BC04BN | Single 8-bit Bus Transceiver |

| DP8400-2 | Error Detection & Correction (EDAC) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DP83957VF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:REPEATER MANAGEMENT|QFP|80PIN|PLASTIC |

| DP83959 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Port Lite Ethernet Repeater Interface Controller |

| DP83959AVUL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Hub Controller |

| DP83959VUL | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Port Lite Ethernet Repeater Interface Controller |

| DP83BC04BJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Single 8-bit Bus Transceiver |

发布紧急采购,3分钟左右您将得到回复。