参数资料

| 型号: | DS1347T+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 3/17页 |

| 文件大小: | 0K |

| 描述: | IC RTC/CALENDAR SPI 8TDFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年,SRAM |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | SPI |

| 电源电压: | 2 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-WDFN 裸露焊盘 |

| 供应商设备封装: | 8-TDFN EP |

| 包装: | 标准包装 |

| 其它名称: | DS1347T+T&RDKR |

Low-Current, SPI-Compatible

Real-Time Clock

Maxim Integrated

11

DS1347

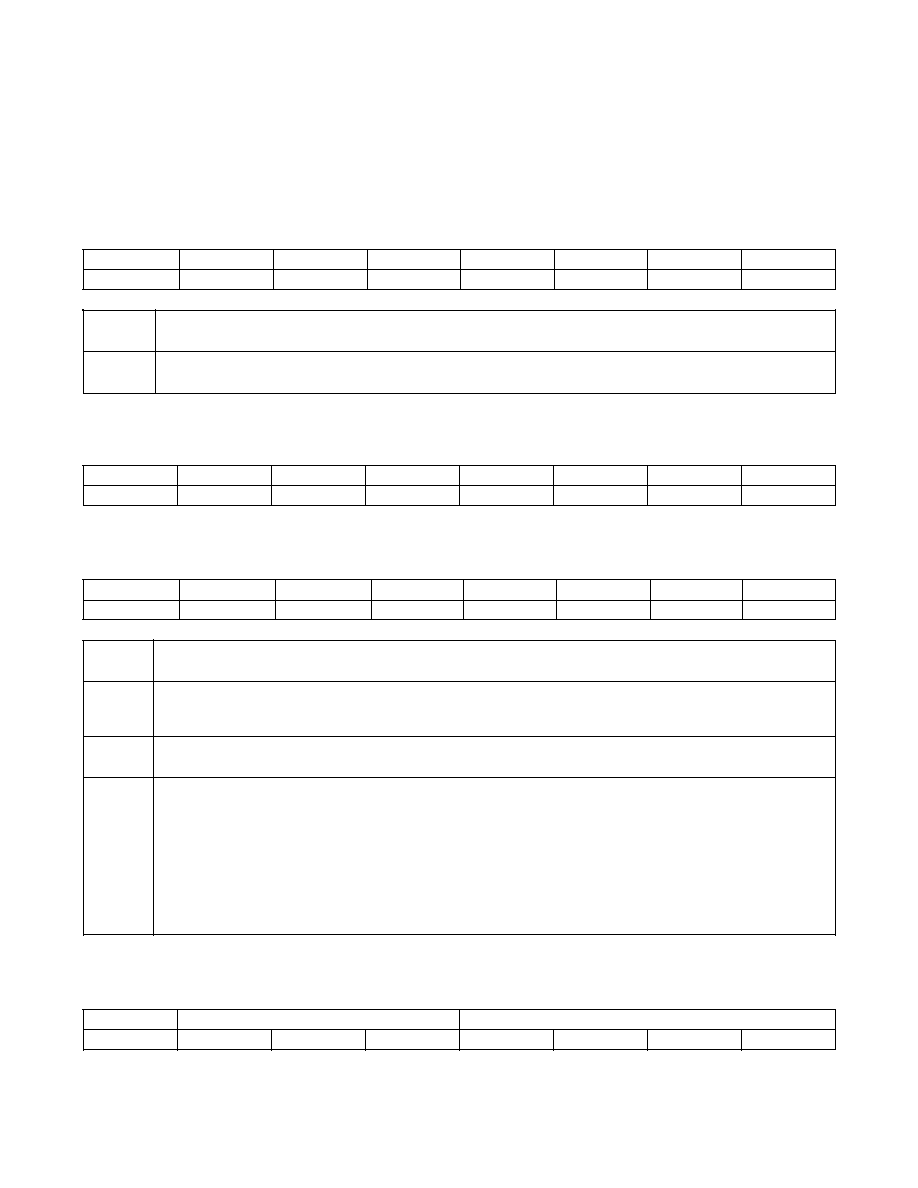

Control Register (0Fh)

Status Register (17h)

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

WP

0

ID

0

BIT 7

WP: Write-Protect RAM. If the WP bit is logic one, writing to the 31 bytes of RAM is inhibited. This bit is cleared

(0) when power is first applied.

BIT 0

ID: Device Identification Bit. The content of this bit does not alter the component functionality. This bit is cleared

(0) when power is first applied.

Alarm Configuration Register (15h)

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

YEAR

DAY

MONTH

DATE

HOUR

MINUTE

SECOND

0

Alarm Seconds Register (19h)

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

10 SECONDS

SECONDS

0

1

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

EOSC

DOSF

EGFIL

0

OSF

0

1

BIT 7

EOSC: Enable Oscillator. When the EOSC bit is logic 0, the oscillator is enabled. When this bit is logic 1, the

oscillator is disabled. This bit is cleared (0) when power is first applied.

BIT 6

DOSF: Disable Oscillator Stop Flag. When the DOSF bit is set to 1, sensing of the oscillator conditions that would

set the OSF bit is disabled. OSF remains at 0 regardless of what happens to the oscillator. This bit is cleared (0)

on the initial application of power.

BIT 5

EGFIL: Enable Glitch Filter. When the EGFIL bit is 1, the 5μs glitch filter at the output of crystal oscillator is

enabled. The glitch filter is disabled when this bit is 0. This bit is cleared (0) on the initial application of power.

BIT 2

OSF: Oscillator Stop Flag. If the OSF bit is 1, the oscillator either has stopped or was stopped for some period and

could be used to judge the validity of the clock and calendar data. This bit is edge triggered and is set to 1 when

the internal circuitry senses the oscillator has transitioned from a normal run state to a stop condition. This bit

remains at logic 1 until written to logic 0. Attempting to write OSF to 1 leaves the value unchanged. The following

are examples of conditions that can cause the OSF bit to be set:

1) The first time power is applied.

2) The voltage present on VCC is insufficient to support oscillation.

3) The

EOSC bit is set to logic 1.

4) External influences on the crystal (i.e., noise, leakage, etc.).

相关PDF资料 |

PDF描述 |

|---|---|

| VI-J5H-MZ | CONVERTER MOD DC/DC 52V 25W |

| VI-23T-MW | CONVERTER MOD DC/DC 6.5V 100W |

| VI-J54-MZ | CONVERTER MOD DC/DC 48V 25W |

| VE-JTP-MZ | CONVERTER MOD DC/DC 13.8V 25W |

| VI-230-MX-B1 | CONVERTER MOD DC/DC 5V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS135 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:1.0A Power Rectifier |

| DS1350AB | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350AB-100 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350AB-70 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4096k Nonvolatile SRAM with Battery Monitor |

| DS1350ABL-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NVRAM (Battery Based) |

发布紧急采购,3分钟左右您将得到回复。