- 您现在的位置:买卖IC网 > PDF目录1914 > DS21352LB (Maxim Integrated Products)IC TXRX 1-CHIP T1 3.3V 100-LQFP PDF资料下载

参数资料

| 型号: | DS21352LB |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 95/137页 |

| 文件大小: | 0K |

| 描述: | IC TXRX 1-CHIP T1 3.3V 100-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS |

| 产品变化通告: | Product Discontinuation 20/Feb/2012 |

| 标准包装: | 90 |

| 功能: | 单芯片收发器 |

| 接口: | HDLC,T1 |

| 电路数: | 1 |

| 电源电压: | 3.14 V ~ 3.47 V |

| 电流 - 电源: | 75mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

| 包括: | DSX-1 和 CSU 线路补偿发生器,HDLC 控制器,带内回路代码发生器和检测器 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页当前第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页

DS21352/DS21552

60 of 137

11.1 TRANSMIT SIDE CODE GENERATION

In the transmit direction there are two methods by which channel data from the backplane can be

overwritten with data generated by the framer. The first method which is covered in Section 11.1 was a

feature contained in the original DS2151 while the second method which is covered in Section 11.2 is a

new feature of the DS2152/352/552.

11.1.1 FIXED PER-CHANNEL IDLE CODE INSERTION

The first method involves using the Transmit Idle Registers (TIR1/2/3) to determine which of the 24 T1

channels should be overwritten with the code placed in the Transmit Idle Definition Register (TIDR).

This method allows the same 8–bit code to be placed into any of the 24 T1 channels. If this method is

used, then the CCR4.0 control bit must be set to zero.

Each of the bit position in the Transmit Idle Registers (TIR1/TIR2/TIR3) represent a DS0 channel in the

outgoing frame. When these bits are set to a one, the corresponding channel will transmit the Idle Code

contained in the Transmit Idle Definition Register (TIDR). Robbed bit signaling and Bit 7 stuffing will

occur over the programmed Idle Code unless the DS0 channel is made transparent by the Transmit

Transparency Registers.

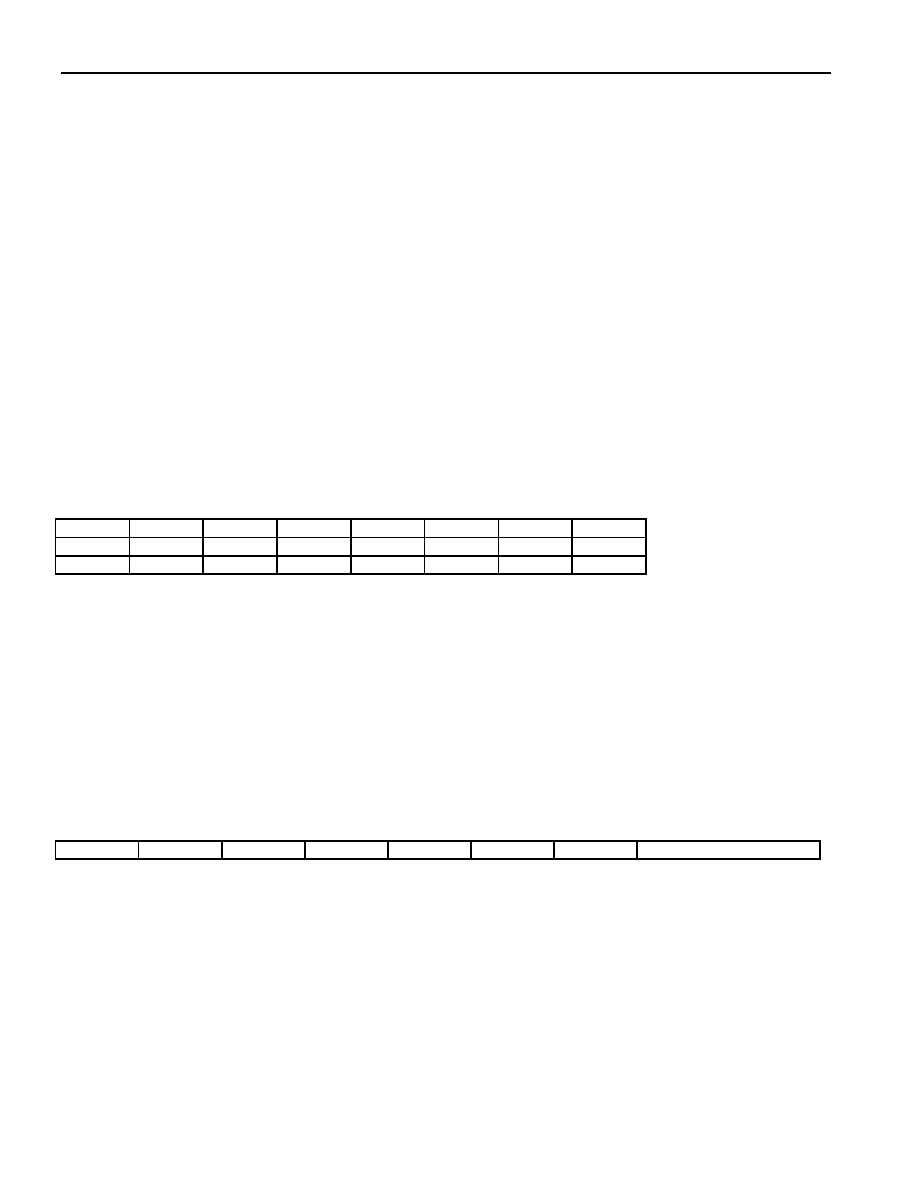

TIR1/TIR2/TIR3: TRANSMIT IDLE REGISTERS (Address=3C to 3E Hex)

[Also used for Per–Channel Loopback]

(MSB)

(LSB)

CH8

CH7

CH6

CH5

CH4

CH3

CH2

CH1

TIR1 (3C)

CH16

CH15

CH14

CH13

CH12

CH11

CH10

CH9

TIR2 (3D)

CH24

CH23

CH22

CH21

CH20

CH19

CH18

CH17

TIR3 (3E)

SYMBOLS

POSITIONS

NAME AND DESCRIPTION

CH1-24

TIR1.0-3.7

Transmit Idle Code Insertion Control Bits.

0 = do not insert the Idle Code in the TIDR into this channel

1 = insert the Idle Code in the TIDR into this channel

NOTE:

If CCR4.0=1, then a zero in the TIRs implies that channel data is to be sourced from TSER and a one

implies that channel data is to be sourced from the output of the receive side framer (i.e., Per–Channel

Loopback; see Figure 3-1.

TIDR: TRANSMIT IDLE DEFINITION REGISTER (Address=3F Hex)

(MSB)

(LSB)

TIDR7

TIDR6

TIDR5

TIDR4

TIDR3

TIDR2

TIDR1

TIDR0

SYMBOL

POSITION

NAME AND DESCRIPTION

TIDR7

TIDR.7

MSB of the Idle Code (this bit is transmitted first)

TIDR0

TIDR.0

LSB of the Idle Code (this bit is transmitted last)

11.1.2 UNIQUE PER-CHANNEL IDLE CODE INSERTION

The second method involves using the Transmit Channel Control Registers (TCC1/2/3) to determine which of the 24 T1

channels should be overwritten with the code placed in the Transmit Channel Registers (TC1 to TC24). This method is more

flexible than the first in that it allows a different 8–bit code to be placed into each of the 24 T1 channels.

相关PDF资料 |

PDF描述 |

|---|---|

| DS21372TN | IC TESTER BIT ERROR 3.3V 32-TQFP |

| DS2141AQN | IC CONTROLLER T1 5V 44-PLCC |

| DS2143QN/T&R | IC CONTROLLER E1 5V LP 44-PLCC |

| DS21448L | IC LIU QUAD E1/T1/J1 128-LQFP |

| DS21455N+ | IC LIU QUAD T1/E1/J1 256-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21352LB+ | 功能描述:网络控制器与处理器 IC T1 Single Chip Transceivers RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21352LBN | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS21352L-C02 | 功能描述:网络控制器与处理器 IC T1 Single Chip Transceivers RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21352LN | 功能描述:网络控制器与处理器 IC T1 Single Chip Transceivers RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21352LN+ | 功能描述:网络控制器与处理器 IC T1 Single Chip Transceivers RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。