- 您现在的位置:买卖IC网 > PDF目录10993 > DS2180AQN/T&R (Maxim Integrated Products)IC TRANSCEIVER T1 IND 44-PLCC PDF资料下载

参数资料

| 型号: | DS2180AQN/T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 14/35页 |

| 文件大小: | 0K |

| 描述: | IC TRANSCEIVER T1 IND 44-PLCC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 500 |

| 功能: | 收发器 |

| 接口: | T1 |

| 电路数: | 1 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 3mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC(16.59x16.59) |

| 包装: | 带卷 (TR) |

| 包括: | 警报生成和检测,B7 填充模式,B8ZS 模式,错误检测和计数器,“硬件”模式,透明模式 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

DS2180A

21 of 35

RYEL OUTPUT

The yellow alarm output transitions high when a yellow alarm is detected. A high-low transition indicates

the alarm condition has been cleared. The RYEL bit (RSR.5) is a “latched” version of the RYEL output.

In 193E framing, the yellow alarm pattern detected is 16 pattern sets of 00 (Hex) and FF (Hex) received

at RLINK. In 193S, framing the yellow alarm format is de-pendent on CCR.3; if CCR.3=0, the RYEL

output transitions high if bit 2 of 256 or more consecutive channels is 0; if CCR.3=1, yellow alarm is

declared when the S-bit received in frame 12 is 1.

RBV OUTPUT

The bipolar violation output transitions high when an accused bit emerges at RSER. RBV will go low at

the next bit time if no additional violations are detected.

RFER OUTPUT

The receive frame error output transitions high at the F-bit time and is held high for two bit periods when

a frame bit error occurs. In 193S framing, FT and FS patterns are tested. The FPS pattern is tested in 193E

framing. Additionally, in 193E framing, RFER reports a CRC error by a low-high-low transition (one bit

period wide) one half RCLK period before a low-high transition on RMSYNC.

RESET

A high-low transition on RST clears all registers and forces immediate receive resync when RST returns

high. This reset has no effect on transmit frame multiframe or channel counters. RST must be held low on

system power-up to insure proper initialization of transceiver counters and registers. Following reset, the

host processor should restore all control modes by writing appropriate registers with control data.

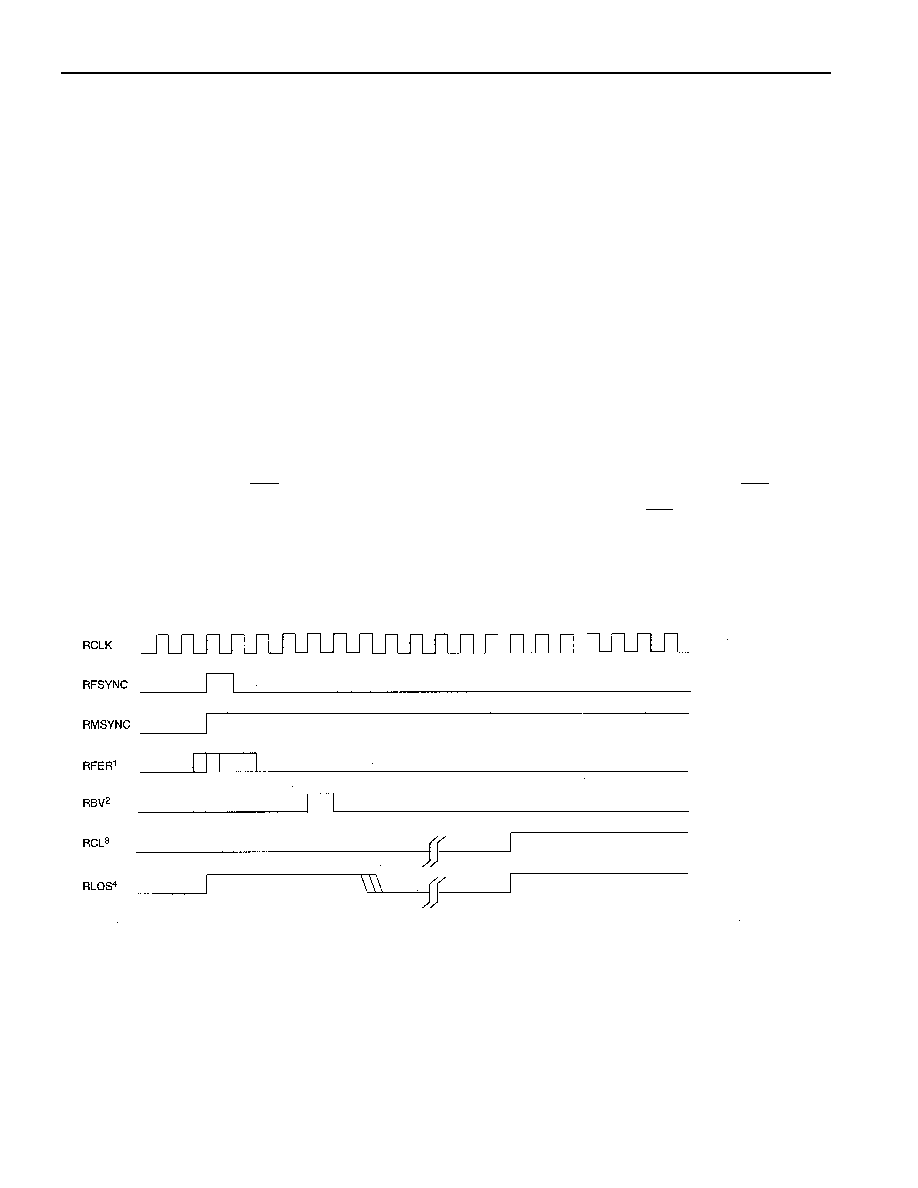

ALARM OUTPUT TIMING Figure 21

NOTES:

1. RFER transitions high during F-bit time if received framing pattern bit is in error. (Frame 12 F-bits in

193S are ignored if CCR.3=1). Also, in 193E, RFER transitions 1/2 bit time before the rising edge of

RMSYNC to indicate a CRC error for the previous multiframe.

2. RBV indicates received bipolar violation and transitions high when an accused bit emerges from

RSER. If B8ZS is enabled, RBV will not report the zero replacement code.

3. RCL transitions high (during 32nd bit time) when 32 consecutive bits received are 0; RCL transitions

low when the next 1 is received.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-24V-IY-B1 | CONVERTER MOD DC/DC 5.8V 50W |

| VI-240-IY-B1 | CONVERTER MOD DC/DC 5V 50W |

| VE-BND-IY-B1 | CONVERTER MOD DC/DC 85V 50W |

| VE-BNB-IY-B1 | CONVERTER MOD DC/DC 95V 50W |

| VE-B6P-IY-B1 | CONVERTER MOD DC/DC 13.8V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2180IND | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| DS2180Q | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM Transceiver |

| DS2180QIND | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| DS2181A | 功能描述:网络控制器与处理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2181A+ | 功能描述:网络控制器与处理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。