- 您现在的位置:买卖IC网 > PDF目录97867 > DS21FT40 (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PBGA300 PDF资料下载

参数资料

| 型号: | DS21FT40 |

| 厂商: | DALLAS SEMICONDUCTOR |

| 元件分类: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PBGA300 |

| 封装: | BGA-300 |

| 文件页数: | 42/87页 |

| 文件大小: | 386K |

| 代理商: | DS21FT40 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

DS21FT40

47 of 87

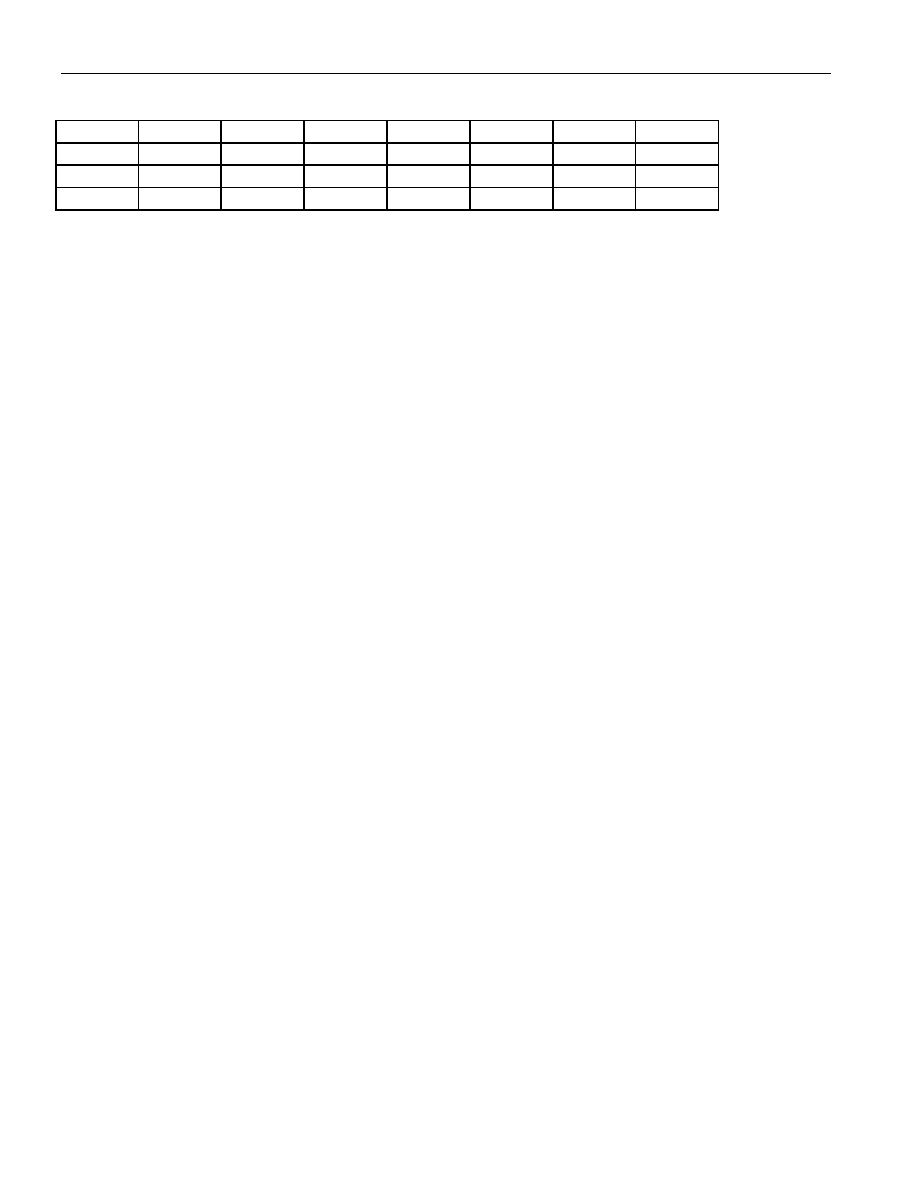

TCBR1/TCBR2/TCBR3/TCBR4: DEFINITION WHEN CCR3.6=1

(MSB)

(LSB)

CH20

CH4

CH19

CH3

CH18

CH2

CH17*

CH1*

TCBR1(22)

CH24

CH8

CH23

CH7

CH22

CH6

CH21

CH5

TCBR2(23)

CH28

CH12

CH27

CH11

CH26

CH10

CH25

CH9

TCBR3(24)

CH32

CH16

CH31

CH15

CH30

CH14

CH29

CH13

TCBR4(25)

*=CH1 and CH17 should be set to one to allow the internal TS1 register to create the CAS Multiframe

Alignment Word and Spare/Remote Alarm bits.

9.2

HARDWARE BASED SIGNALING

Receive Side

Hardware signaling is supported through a mode called signaling re-insertion which is invoked by setting

the RSRE control bit high (CCR3.3=1). In this mode, the user will provide a multiframe sync at the

RSYNC pin and the signaling data will be re-aligned at the RSER output according to this applied

multiframe boundary. In this mode, the elastic store must be enabled and the backplane clock must be

2.048 MHz.

The signaling data in the two multiframe buffer will be frozen in a known good state upon either a loss of

synchronization (OOF event), carrier loss, or frame slip. To allow this freeze action to occur, the RFE

control bit (CCR2.0) should be set high. The user can force a freeze by setting the RFF control bit

(CCR2.1) high. Setting the RFF bit high causes the same freezing action as if a loss of synchronization,

carrier loss, or slip has occurred.

The 2 multiframe buffer provides an approximate 1 multiframe delay in the signaling bits provided at the

RSER pin (if RSRE=1 via CCR3.3). When freezing is enabled (RFE=1), the signaling data will be held

in the last known good state until the corrupting error condition subsides. When the error condition sub-

sides, the signaling data will be held in the old state for an additional 3 ms to 5 ms before being allowed

to be updated with new signaling data.

10.

PER–CHANNEL CODE GENERATION AND LOOPBACK

Each framer in the DS21FT40 can replace data on a channel–by–channel basis in both the transmit and

receive directions. The transmit direction is from the backplane to the E1 line and is covered in Section

10.1. The receive direction is from the E1 line to the backplane and is covered in Section 10.2.

10.1 TRANSMIT SIDE CODE GENERATION

In the transmit direction there are two methods by which channel data from the backplane can be

overwritten with data generated by the framer. The first method which is covered in Section 10.1.1 was a

feature contained in the original DS21Q43 while the second method which is covered in Section 10.1.2 is

a new feature of the DS21Q44.

10.1.1

Simple Idle Code Insertion and Per–Channel Loopback

The first method involves using the Transmit Idle Registers (TIR1/2/3/4) to determine which of the 32 E1

channels should be overwritten with the code placed in the Transmit Idle Definition Register (TIDR).

相关PDF资料 |

PDF描述 |

|---|---|

| DS21FT42 | DATACOM, FRAMER, PBGA300 |

| DS21FT42N | DATACOM, FRAMER, PBGA300 |

| DS21FF42 | DATACOM, FRAMER, PBGA300 |

| DS21FF42N | DATACOM, FRAMER, PBGA300 |

| DS21FT44N | DATACOM, FRAMER, PBGA300 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21FT40N | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS21FT42 | 功能描述:网络控制器与处理器 IC 4x4 16/4x3 12 Chnl T1/T1 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21FT42N | 功能描述:网络控制器与处理器 IC 4x4 16/4x3 12 Chnl T1/T1 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21FT44 | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21FT44+ | 功能描述:网络控制器与处理器 IC 4X3 E1 Framer E1 Framer E1 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。