- 您现在的位置:买卖IC网 > Datasheet目录323 > DS3065WP-100IND+ (Maxim Integrated Products)IC SRAM 3.3V 8MB 34POWERCAP MOD Datasheet资料下载

参数资料

| 型号: | DS3065WP-100IND+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 10/15页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 3.3V 8MB 34POWERCAP MOD |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 40 |

| 格式 - 存储器: | RAM |

| 存储器类型: | NVSRAM(非易失 SRAM) |

| 存储容量: | 8M(1M x 8) |

| 速度: | 100ns |

| 接口: | 并联 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 34-PowerCap? 模块 |

| 供应商设备封装: | 34-PowerCap 模块 |

| 包装: | 托盘 |

| 其它名称: | 90-3065W+P1I |

�� �

�

�

�DS3065WP�

�3.3V,� 8Mb,� Nonvolatile� SRAM� with� Clock�

�Detailed� Description�

�The� DS3065WP� is� an� 8Mb� (1024k� x� 8� bits),� fully� static,�

�nonvolatile� (NV)� memory� similar� in� function� and� organiza-�

�tion� to� the� DS1265W� NV� SRAM,� but� containing� an� RTC.�

�The� device� NV� SRAM� constantly� monitors� V� CC� for� an� out-�

�of-tolerance� condition.� When� such� a� condition� occurs,�

�the� lithium� energy� source� is� automatically� switched� on�

�and� write� protection� is� unconditionally� enabled� to� prevent�

�data� corruption.� There� is� no� limit� to� the� number� of� write�

�cycles� that� can� be� executed,� and� no� additional� support�

�circuitry� is� required� for� microprocessor� interfacing.� This�

�device� can� be� used� in� place� of� SRAM,� EEPROM,� or� flash�

�components.�

�User� access� to� either� the� SRAM� or� the� RTC� registers� is�

�accomplished� with� a� byte-wide� interface� and� discrete�

�control� inputs,� allowing� for� a� direct� interface� to� many�

�3.3V� microprocessor� devices.�

�The� RTC� contains� a� full-function� clock/calendar� with� an�

�RTC� alarm,� battery� monitor,� and� power� monitor.� RTC�

�registers� contain� century,� year,� month,� date,� day,� hours,�

�minutes,� and� seconds� data� in� a� 24-hour� BCD� format.�

�Corrections� for� day� of� the� month� and� leap� year� are� made�

�automatically.�

�The� RTC� registers� are� double-buffered� into� an� internal�

�and� external� set.� The� user� has� direct� access� to� the� exter-�

�nal� set.� Clock/calendar� updates� to� the� external� set� of�

�registers� can� be� disabled� and� enabled� to� allow� the� user�

�to� access� static� data.� Assuming� the� internal� oscillator� is�

�on,� the� internal� registers� are� continually� updated,� regard-�

�less� of� the� state� of� the� external� registers,� assuring� that�

�accurate� RTC� information� is� always� maintained.�

�The� device� constantly� monitors� the� voltage� of� the� internal�

�battery.� The� battery-low� flag� (BLF)� in� the� RTC� FLAGS�

�read.� Should� a� 1� ever� be� present,� the� battery� voltage� is�

�below� ~� 2V� and� the� contents� of� the� clock� and� SRAM� are�

�questionable.�

�The� device� module� is� constructed� on� a� standard� 34-pin�

�PowerCap� substrate.�

�SRAM� Read� Mode�

�The� device� executes� an� SRAM� read� cycle� whenever� CS�

�(RTC� chip� select)� and� WE� (write� enable)� are� inactive�

�(high)� and� CE� (SRAM� chip� enable)� is� active� (low).� The�

�unique� address� specified� by� the� 20� address� inputs�

�(A0–A19)� defines� which� of� the� 1,048,576� bytes� of� SRAM�

�data� is� to� be� accessed.� Valid� data� is� available� to� the�

�eight� data-output� drivers� within� t� ACC� (access� time)� after�

�the� last� address� input� signal� is� stable,� provided� that� CE�

�and� OE� (output� enable)� access� times� are� also� satisfied.�

�If� CE� and� OE� access� times� are� not� satisfied,� data� access�

�must� be� measured� from� the� later� occurring� signal� (� CE� or�

�OE� ),� and� the� limiting� parameter� is� either� t� CO� for� CE� or�

�t� OE� for� OE� rather� than� address� access.�

�SRAM� Write� Mode�

�The� device� executes� an� SRAM� write� cycle� whenever� CS�

�is� inactive� (high)� and� the� CE� and� WE� signals� are� active�

�(low)� after� address� inputs� are� stable.� The� later-occurring�

�falling� edge� of� CE� or� WE� determines� the� start� of� the� write�

�cycle.� The� write� cycle� is� terminated� by� the� earlier� rising�

�edge� of� CE� or� WE� .� All� address� inputs� must� be� kept� valid�

�throughout� the� write� cycle.� WE� must� return� to� the� high�

�state� for� a� minimum� recovery� time� (t� WR� )� before� another�

�cycle� can� be� initiated.� The� CS� and� OE� control� signal�

�should� be� kept� inactive� (high)� during� SRAM� write� cycles�

�to� avoid� bus� contention.� However,� if� the� output� drivers�

�have� been� enabled� (� CE� and� OE� active),� WE� disables� the�

�outputs� in� t� ODW� from� its� falling� edge.�

�register� is� not� writable� and� should� always� be� a� 0� when�

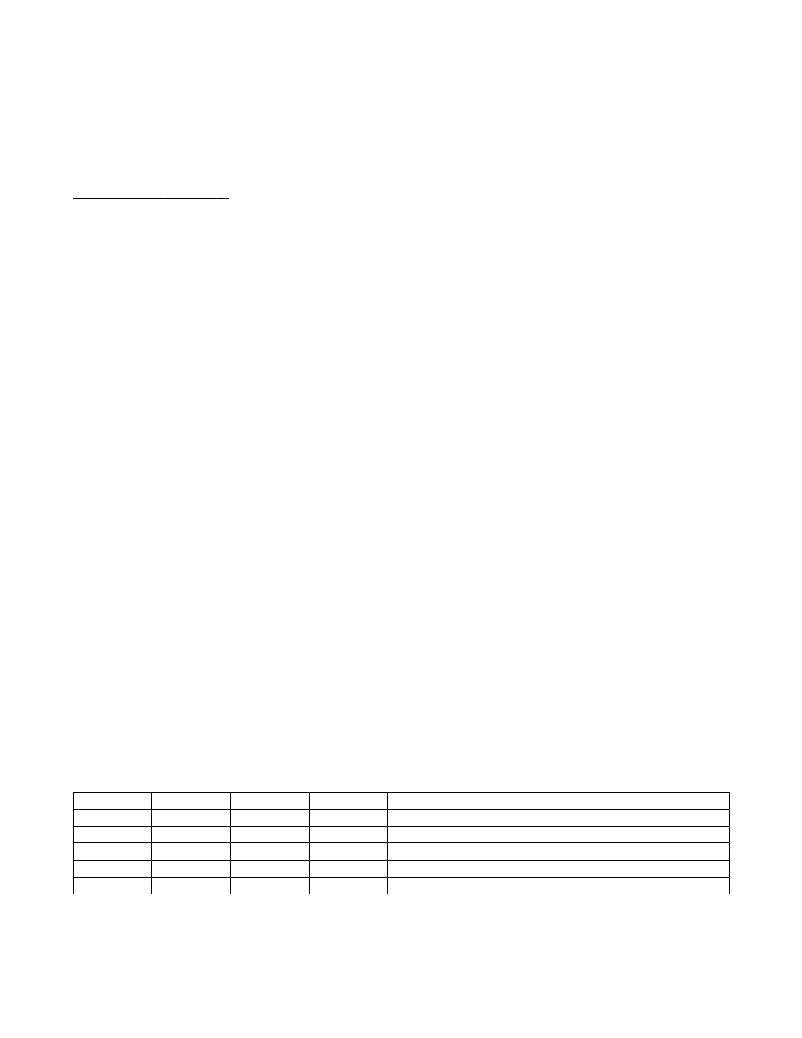

�Table� 1.� RTC/Memory� Operational� Truth� Table�

�CS�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�WE�

�1�

�1�

�0�

�1�

�1�

�0�

�X�

�X�

�CE�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�0�

�OE�

�0�

�1�

�X�

�0�

�1�

�X�

�X�

�X�

�MODE�

�RTC� Read�

�RTC� Read�

�RTC� Write�

�SRAM� Read�

�SRAM� Read�

�SRAM� Write�

�Standby�

�Invalid�

�(see� Figure� 2)�

�ICC�

�Active�

�Active�

�Active�

�Active�

�Active�

�Active�

�Standby�

�Active�

�OUTPUTS�

�Active�

�High� Impedance�

�High� Impedance�

�Active�

�High� Impedance�

�High� Impedance�

�High� Impedance�

�Invalid�

�X� =� Don’t� care.�

�10�

�Maxim� Integrated�

�相关PDF资料 |

PDF描述 |

|---|---|

| DS3070W-100# | IC NVSRAM 16MBIT 100NS 256BGA |

| DS321X | KIT X-WIDE DESIGN STRIP VERT |

| DS323X | KIT X-WIDE DESIGN STRIP VERT |

| DS87001-E52 | ADAPTER MCU 52-TQFP TO 40-DIP |

| DS89C450-K00 | EVAL KIT FOR DS89C450 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3065WP-100IND+ | 功能描述:NVRAM 1.2-5.5V 15kV ESD Pro 8Ch Level RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube |

| DS307 | 功能描述:插线板 DESIGN STRIP KIT RoHS:否 制造商:Switchcraft 产品类型:Bantam (TT) 正规化: 高度/机架数量: 深度: 端接类型: 位置/触点数量:48 |

| DS3070W | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V Single-Piece 16Mb Nonvolatile SRAM with Clock |

| DS3070W-100 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V Single-Piece 16Mb Nonvolatile SRAM with Clock |

| DS3070W-100# | 功能描述:NVRAM RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。