- 您现在的位置:买卖IC网 > PDF目录11562 > DS31256 (Maxim Integrated Products)IC CTRLR HDLC 256-CHANNEL 256BGA PDF资料下载

参数资料

| 型号: | DS31256 |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 29/183页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR HDLC 256-CHANNEL 256BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 40 |

| 控制器类型: | HDLC 控制器 |

| 接口: | 串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 电流 - 电源: | 500mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BBGA |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页

DS31256 256-Channel, High-Throughput HDLC Controller

124 of 183

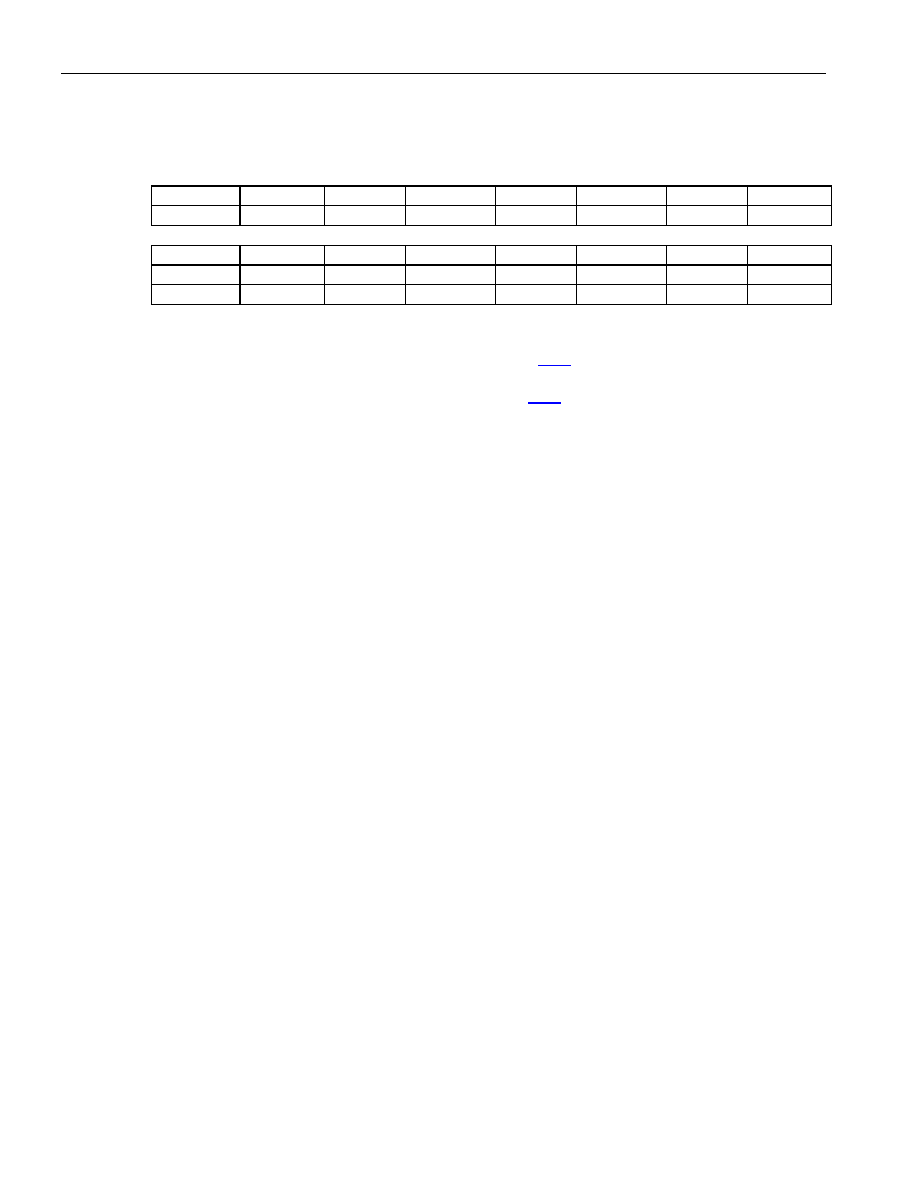

Register Name:

TDMAQ

Register Description:

Transmit DMA Queues Control

Register Address:

0880h

Bit #

7

6

5

4

3

2

1

0

Name

n/a

TDQF

TDQFE

TPQF

TPQFE

Default

0

Bit #

15

14

13

12

11

10

9

8

Name

n/a

TDQT2

TDQT1

TDQT0

Default

0

Note: Bits that are underlined are read-only; all other bits are read-write.

Bit 0/Transmit Pending-Queue FIFO Enable (TPQFE). See Section 9.3.3 for details.

Bit 1/Transmit Pending-Queue FIFO Flush (TPQLF). See Section 9.3.3 for details.

Bit 3/Transmit Done-Queue FIFO Enable (TDQFE). This bit must be set to 1 to enable the DMA to burst write

descriptors to the done queue. If this bit is set to 0, descriptors are written one at a time.

0 = done-queue burst write disabled

1 = done-queue burst write enabled

Bit 4/Transmit Done-Queue FIFO Flush (TDQF). When this bit is set to 1, the internal done-queue FIFO is

flushed by sending all data into the done queue. This bit must be set to 0 for proper operation.

0 = FIFO in normal operation

1 = FIFO is flushed

Bits 8 to 10/Transmit Done-Queue Status Bit Threshold Setting (TDQT0 to TDQT2). These bits determine

when the DMA sets the transmit DMA done-queue write (TDQW) status bit in the status register for DMA

(SDMA) register.

000 = set the TDQW status bit after each descriptor write to the done queue

001 = set the TDQW status bit after 2 or more descriptors are written to the done queue

010 = set the TDQW status bit after 4 or more descriptors are written to the done queue

011 = set the TDQW status bit after 8 or more descriptors are written to the done queue

100 = set the TDQW status bit after 16 or more descriptors are written to the done queue

101 = set the TDQW status bit after 32 or more descriptors are written to the done queue

110 = set the TDQW status bit after 64 or more descriptors are written to the done queue

111 = set the TDQW status bit after 128 or more descriptors are written to the done queue

相关PDF资料 |

PDF描述 |

|---|---|

| DS3112N | IC MUX TEMPE T3/E3 IND 256-BGA |

| CONREVSMA002-SMD | CONN RP-SMA FEMALE R-A SMD |

| DS21FT44N | IC FRAMER E1 4X3 12CH IND 300BGA |

| PIC16F1933-E/SP | MCU 8BIT 4K FLASH 28-DIP |

| DS21FF42+ | IC FRAMER T1 4X4 16CH 300-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS31256+ | 功能描述:输入/输出控制器接口集成电路 256Ch High Thruput HDLC Cntlr RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray |

| DS31256B | 功能描述:输入/输出控制器接口集成电路 256Ch High Thruput HDLC Cntlr RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray |

| DS31256DK | 功能描述:网络开发工具 RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V |

| DS31256-W+ | 制造商:Maxim Integrated Products 功能描述:ENVOY 256 CHANNEL HDLC - WAIVER - Rail/Tube |

| DS312BNC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

发布紧急采购,3分钟左右您将得到回复。