- 您现在的位置:买卖IC网 > PDF目录3834 > DSPIC30F3011-30I/P (Microchip Technology)IC DSPIC MCU/DSP 24K 40DIP PDF资料下载

参数资料

| 型号: | DSPIC30F3011-30I/P |

| 厂商: | Microchip Technology |

| 文件页数: | 123/228页 |

| 文件大小: | 0K |

| 描述: | IC DSPIC MCU/DSP 24K 40DIP |

| 产品培训模块: | dsPIC30F Quadrature Encoder Interface Serial Communications using dsPIC30F I2C Serial Communications using dsPIC30F SPI Serial Communications using dsPIC30F UART dsPIC30F 12 bit ADC - Part 2 dsPIC30F Addressing Modes - Part 1 dsPIC30F Architecture - Part 1 dsPIC30F DSP Engine & ALU dsPIC30F Interrupts dsPIC30F Motor Control PWM dsPIC Timers Asynchronous Stimulus dsPIC30F Addressing Modes - Part 2 dsPIC30F Architecture - Part 2 dsPIC30F 12-bit ADC Part 1 |

| 标准包装: | 10 |

| 系列: | dsPIC™ 30F |

| 核心处理器: | dsPIC |

| 芯体尺寸: | 16-位 |

| 速度: | 30 MIP |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | 高级欠压探测/复位,电机控制 PWM,QEI,POR,PWM,WDT |

| 输入/输出数: | 30 |

| 程序存储器容量: | 24KB(8K x 24) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 1K x 8 |

| RAM 容量: | 1K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.5 V ~ 5.5 V |

| 数据转换器: | A/D 9x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 包装: | 管件 |

| 产品目录页面: | 651 (CN2011-ZH PDF) |

| 配用: | AC30F003-ND - MODULE SOCKET DSPIC30F 40DIP DV164005-ND - KIT ICD2 SIMPLE SUIT W/USB CABLE ACICE0206-ND - ADAPTER MPLABICE 40P 600 MIL |

| 其它名称: | DSPIC30F3011-30IP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页当前第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页

209

XMEGA A [MANUAL]

8077I–AVR–11/2012

A high-to-low transition on the SCL line will force the line low for all masters on the bus, and they will start timing their low

clock period. The timing length of the low clock period can vary among the masters. When a master (DEVICE1 in this

case) has completed its low period, it releases the SCL line. However, the SCL line will not go high until all masters have

released it. Consequently, the SCL line will be held low by the device with the longest low period (DEVICE2). Devices

with shorter low periods must insert a wait state until the clock is released. All masters start their high period when the

SCL line is released by all devices and has gone high. The device which first completes its high period (DEVICE1) forces

the clock line low, and the procedure is then repeated. The result is that the device with the shortest clock period

determines the high period, while the low period of the clock is determined by the device with the longest clock period.

19.4

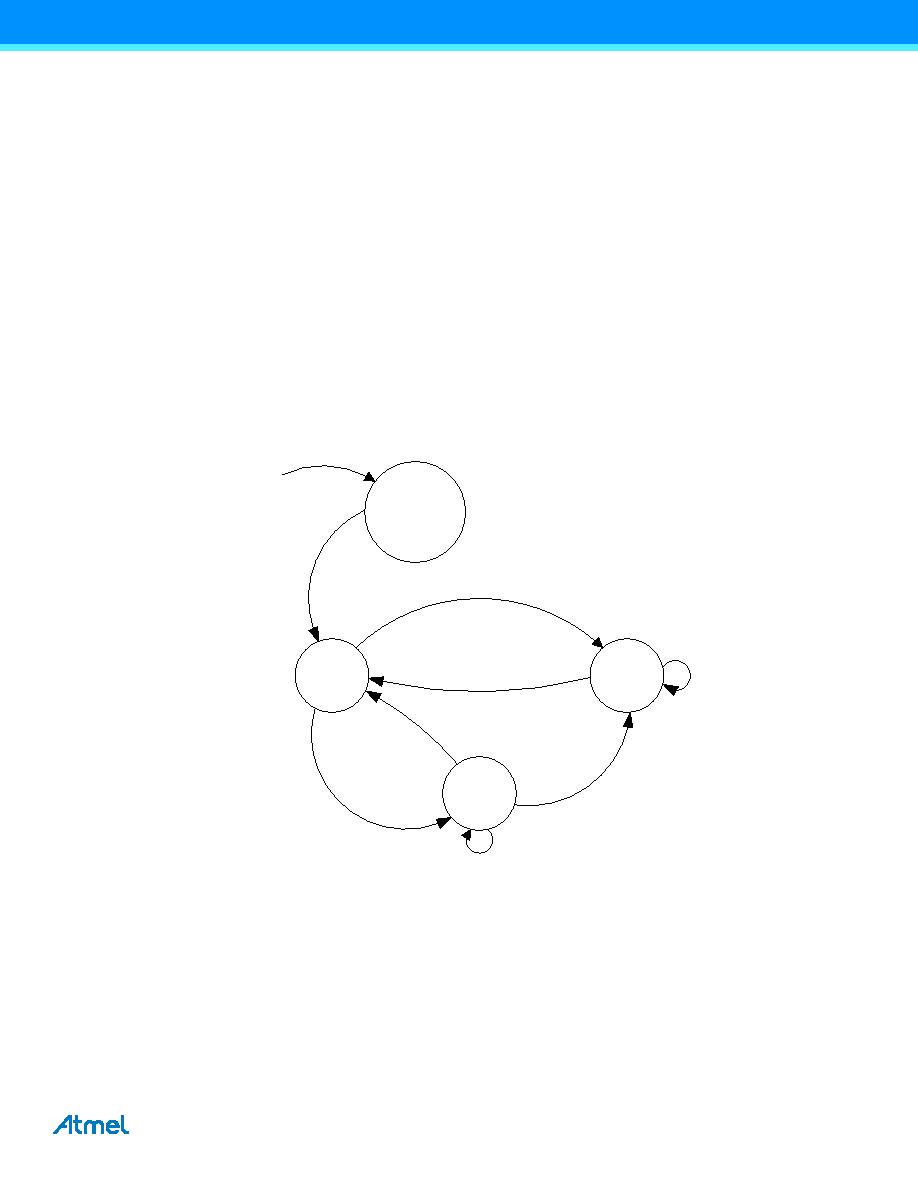

TWI Bus State Logic

The bus state logic continuously monitors the activity on the TWI bus lines when the master is enabled. It continues to

operate in all sleep modes, including power-down.

The bus state logic includes START and STOP condition detectors, collision detection, inactive bus timeout detection,

and a bit counter. Theseare used to determine the bus state. Software can get the current bus state by reading the bus

state bits in the master status register. The bus state can be unknown, idle, busy, or owner, and is determined according

to the state diagram shown in Figure 19-11. The values of the bus state bits according to state are shown in binary in the

figure.

Figure 19-11.Bus state, state diagram.

After a system reset and/or TWI master enable, the bus state is unknown. The bus state machine can be forced to enter

idle by writing to the bus state bits accordingly. If no state is set by application software, the bus state will become idle

when the first STOP condition is detected. If the master inactive bus timeout is enabled, the bus state will change to idle

on the occurrence of a timeout. After a known bus state is established, only a system reset or disabling of the TWI master

will set the state to unknown.

When the bus is idle, it is ready for a new transaction. If a START condition generated externally is detected, the bus

becomes busy until a STOP condition is detected. The STOP condition will change the bus state to idle. If the master

inactive bus timeout is enabled, the bus state will change from busy to idle on the occurrence of a timeout.

If a START condition is generated internally while in idle state, the owner state is entered. If the complete transaction was

performed without interference, i.e., no collisions are detected, the master will issue a STOP condition and the bus state

P + Timeout

Write ADDRESS

IDLE

(0b01)

S

BUSY

(0b11)

UNKNOWN

(0b00)

OWNER

(0b10)

Arbitration

Lost

Command P

Write

ADDRESS(Sr)

Sr

(S)

RESET

P + Timeout

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16LF873A-I/SP | IC MCU FLASH 4KX14 EE A/D 28DIP |

| AT89C51AC3-RLTIM | IC 8051 MCU FLASH 64K 44VQFP |

| PIC16LF873A-I/SO | IC MCU FLASH 4KX14 EE A/D 28SOIC |

| AT89C51AC3-RDTIM | IC 8051 MCU FLASH 64K 64VQFP |

| PIC16F84-04/P | IC MCU FLASH 1KX14 EE 18DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| dsPIC30F3011T-20E/ML | 功能描述:数字信号处理器和控制器 - DSP, DSC 44LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| dsPIC30F3011T-20E/PT | 功能描述:数字信号处理器和控制器 - DSP, DSC 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| DSPIC30F3011T-20I/ML | 功能描述:IC DSPIC MCU/DSP 24K 44QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:dsPIC™ 30F 产品培训模块:XLP Deep Sleep Mode 8-bit PIC® Microcontroller Portfolio 标准包装:22 系列:PIC® XLP™ 18F 核心处理器:PIC 芯体尺寸:8-位 速度:48MHz 连通性:I²C,SPI,UART/USART,USB 外围设备:欠压检测/复位,POR,PWM,WDT 输入/输出数:14 程序存储器容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 大小:256 x 8 RAM 容量:512 x 8 电压 - 电源 (Vcc/Vdd):1.8 V ~ 5.5 V 数据转换器:A/D 11x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:20-DIP(0.300",7.62mm) 包装:管件 产品目录页面:642 (CN2011-ZH PDF) 配用:DV164126-ND - KIT DEVELOPMENT USB W/PICKIT 2DM164127-ND - KIT DEVELOPMENT USB 18F14/13K50AC164112-ND - VOLTAGE LIMITER MPLAB ICD2 VPP |

| DSPIC30F3011T-20I/PT | 功能描述:IC DSPIC MCU/DSP 24K 44TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:dsPIC™ 30F 产品培训模块:XLP Deep Sleep Mode 8-bit PIC® Microcontroller Portfolio 标准包装:22 系列:PIC® XLP™ 18F 核心处理器:PIC 芯体尺寸:8-位 速度:48MHz 连通性:I²C,SPI,UART/USART,USB 外围设备:欠压检测/复位,POR,PWM,WDT 输入/输出数:14 程序存储器容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 大小:256 x 8 RAM 容量:512 x 8 电压 - 电源 (Vcc/Vdd):1.8 V ~ 5.5 V 数据转换器:A/D 11x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:20-DIP(0.300",7.62mm) 包装:管件 产品目录页面:642 (CN2011-ZH PDF) 配用:DV164126-ND - KIT DEVELOPMENT USB W/PICKIT 2DM164127-ND - KIT DEVELOPMENT USB 18F14/13K50AC164112-ND - VOLTAGE LIMITER MPLAB ICD2 VPP |

| dsPIC30F3011T-30I/ML | 功能描述:数字信号处理器和控制器 - DSP, DSC 44LD 30MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。