- 您现在的位置:买卖IC网 > PDF目录93349 > EDI88130CS 128Kx8 Monolithic SRAM(128Kx8 CMOS单片静态RAM) PDF资料下载

参数资料

| 型号: | EDI88130CS |

| 英文描述: | 128Kx8 Monolithic SRAM(128Kx8 CMOS单片静态RAM) |

| 中文描述: | 128Kx8单片的SRAM(128Kx8的CMOS单片静态内存) |

| 文件页数: | 3/9页 |

| 文件大小: | 255K |

| 代理商: | EDI88130CS |

3

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

EDI88130CS

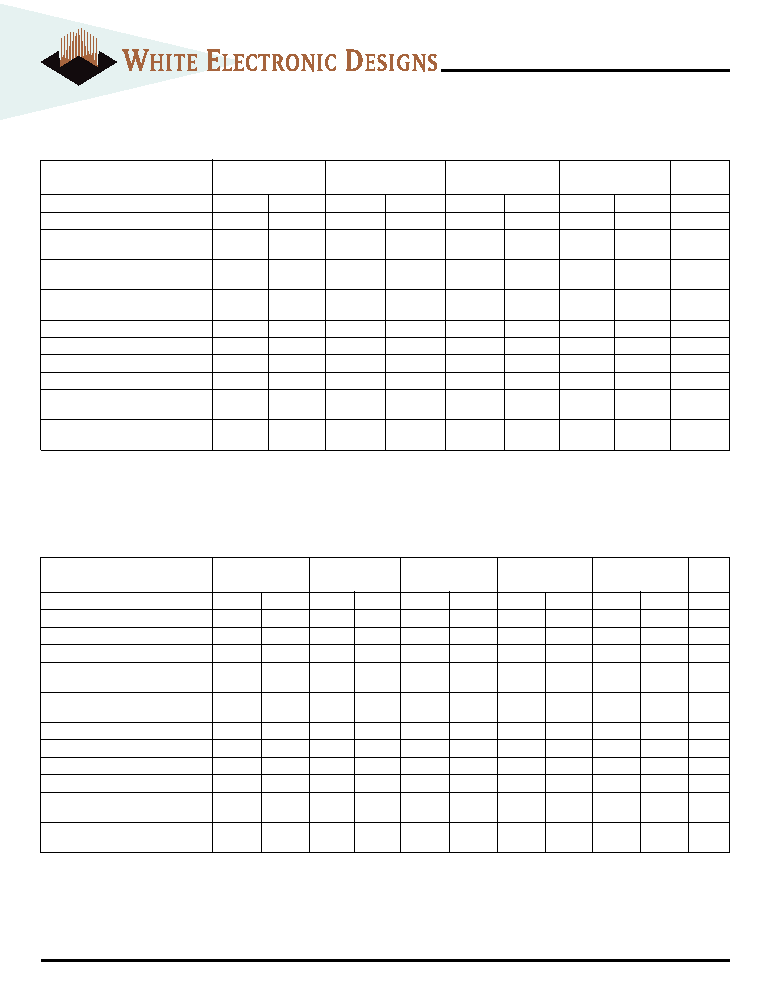

AC CHARACTERISTICS – READ CYCLE (15 to 20ns)

(VCC = 5.0V, VSS = 0V, TA = -55

°C to +125°C)

Symbol

15ns*

17ns

20ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Min

Max

Units

Read Cycle Time

tAVAV

tRC

15

17

20

ns

Address Access Time

tAVQV

tAA

15

17

20

ns

Chip Enable Access Time

tE1LQV

tACS

15

17

20

ns

tE2HQV

tACS

15

17

20

ns

Chip Enable to Output in Low Z (1)

tE1LQX

tCLZ

55

5

ns

tE2HQX

tCLZ

55

5

ns

Chip Disable to Output in Low Z (1)

tE1HQZ

tCHZ

67

8

ns

tE2LQZ

tCHZ

67

8

ns

Output Hold from Address Change

tAVQX

tOH

33

3

ns

Output Enable to Output Valid

tGLQV

tOE

66

7

ns

Output Enable to Output in Low Z (1)

tGLQX

tOLZ

00

0

ns

Output Disable to Output in High Z(1)

tGHQZ

tOHZ

56

8

ns

Chip Enable to Power Up (1)

tE1LICCH

tPU

00

0

ns

tE2HICCH

tPU

00

0

ns

Chip Enable to Power Down (1)

tE1HICCL

tPD

15

17

20

ns

tE2LICCL

tPD

15

17

20

ns

1. This parameter is guaranteed by design but not tested.

* 15ns access time is advanced information, contact factory for availability.

AC CHARACTERISTICS – READ CYCLE (25 to 55ns)

(VCC = 5.0V, VSS = 0V, TA = -55

°C to +125°C)

Symbol

25ns

35ns

45ns

55ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Min

Max

Min

Max

Units

Read Cycle Time

tAVAV

tRC

25

35

45

55

ns

Address Access Time

tAVQV

tAA

25

35

45

55

ns

Chip Enable Access Time

tE1LQV

tACS

25

35

45

55

ns

Chip Enable Access Time

tE2HQV

tACS

25

35

45

55

ns

Chip Enable to Output in Low Z (1)

tE1LQX

tCLZ

5555

ns

tE2HQX

tCLZ

5555

ns

Chip Disable to Output in Low Z (1)

tE1HQZ

tCHZ

10

15

20

ns

tE2LQZ

tCHZ

10

15

20

ns

Output Hold from Address Change

tAVQX

tOH

0000

ns

Output Enable to Output Valid

tGLQV

tOE

10

15

20

25

ns

Output Enable to Output in Low Z (1)

tGLQX

tOLZ

0000

ns

Output Disable to Output in High Z(1)

tGHQZ

tOHZ

10

15

20

ns

Chip Enable to Power Up (1)

tE1LICCH

tPU

0000

ns

tE2HICCH

tPU

0000

ns

Chip Enable to Power Down (1)

tE1HICCL

tPD

25

35

45

55

ns

tE2LICCL

tPD

25

35

45

55

ns

1. This parameter is guaranteed by design but not tested.

相关PDF资料 |

PDF描述 |

|---|---|

| EDI88257CA | 256Kx8 Monolithic SRAM(256Kx8 CMOS单片静态RAM(存取时间20,25,35,45,55ns)) |

| EDI88257C | 256Kx8 Monolithic SRAM(256Kx8 CMOS单片静态RAM(存取时间70,85,100ns)) |

| EDI88512CA-RP | 512Kx8 Plastic Monolithic SRAM CMOS(512Kx8 CMOS塑料单片静态RAM) |

| EDI88512CA | 512Kx8 Monolithic SRAM(512Kx8 CMOS单片静态RAM) |

| EDI88512C | 512Kx8 Monolithic SRAM(512Kx8 CMOS单片静态RAM) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EDI88130CS/LPS-C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SRAM |

| EDI88130CS/LPS-F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SRAM |

| EDI88130CS/LPS-N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SRAM |

| EDI88130CS/LPS-T | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SRAM |

| EDI88130CS12CB | 制造商:Microsemi Corporation 功能描述:128K X 8 SRAM MONOLITHIC, DUAL CHIP SELECT, 5V, 12NS, 32 DIP - Bulk |

发布紧急采购,3分钟左右您将得到回复。