- 您现在的位置:买卖IC网 > PDF目录18702 > EFM32-TG822F32-SK (Energy Micro)IC MICRO KIT GECKO 48LQFP PDF资料下载

参数资料

| 型号: | EFM32-TG822F32-SK |

| 厂商: | Energy Micro |

| 文件页数: | 12/136页 |

| 文件大小: | 0K |

| 描述: | IC MICRO KIT GECKO 48LQFP |

| 标准包装: | 1 |

| 系列: | Tiny Gecko |

| 套件类型: | 微控制器 |

| 值: | 2 件 - 闪存 - 32KB |

| 包装: | 纸板盒 |

| 安装类型: | 表面贴装 |

| 包括封装: | 48-LQFP |

| 其它名称: | 914-1023 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

...the world's most energy friendly microcontrollers

2011-02-04 - d0002_Rev1.00

109

www.energymicro.com

Bits

Name

Function

When this bit is set to 1, the PC value stacked for the exception return points to the instruction

that tried to perform the illegal load of the PC.

[1]

INVSTATE

Invalid state usage fault:

0 = no invalid state usage fault

1 = the processor has attempted to execute an instruction that makes illegal use of the EPSR.

When this bit is set to 1, the PC value stacked for the exception return points to the instruction

that attempted the illegal use of the EPSR.

This bit is not set to 1 if an undefined instruction uses the EPSR.

[0]

UNDEFINSTR

Undefined instruction usage fault:

0 = no undefined instruction usage fault

1 = the processor has attempted to execute an undefined instruction.

When this bit is set to 1, the PC value stacked for the exception return points to the undefined

instruction.

An undefined instruction is an instruction that the processor cannot decode.

Note

The UFSR bits are sticky. This means as one or more fault occurs, the associated bits are

set to 1. A bit that is set to 1 is cleared to 0 only by writing 1 to that bit, or by a reset.

4.3.12 Hard Fault Status Register

The HFSR gives information about events that activate the hard fault handler. See the register summary

in Table 4.12 (p. 94) for its attributes.

This register is read, write to clear. This means that bits in the register read normally, but writing 1 to

any bit clears that bit to 0. The bit assignments are:

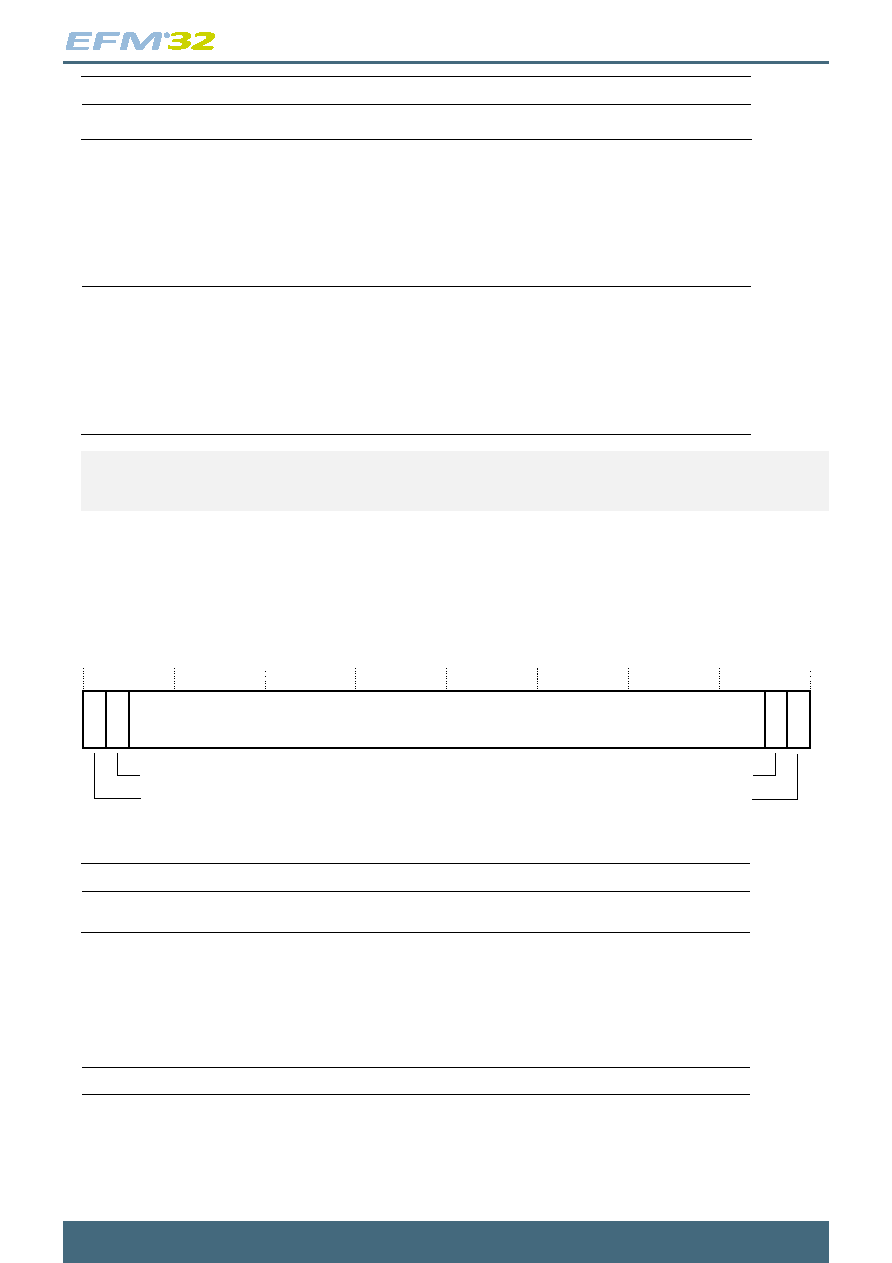

31 30

2 1 0

Reserved

29

DEBUGEVT

FORCED

VECTTBL

Reserved

Table 4.29. HFSR bit assignments

Bits

Name

Function

[31]

DEBUGEVT

Reserved for Debug use. When writing to the register you must write 0 to this bit, otherwise

behavior is Unpredictable.

[30]

FORCED

Indicates a forced hard fault, generated by escalation of a fault with configurable priority that

cannot be handles, either because of priority or because it is disabled:

0 = no forced hard fault

1 = forced hard fault.

When this bit is set to 1, the hard fault handler must read the other fault status registers to find

the cause of the fault.

[29:2]

-

Reserved.

[1]

VECTTBL

Indicates a bus fault on a vector table read during exception processing:

0 = no bus fault on vector table read

1 = bus fault on vector table read.

This error is always handled by the hard fault handler.

相关PDF资料 |

PDF描述 |

|---|---|

| EFM32-TG222F32-SK | IC MICRO KIT GECKO 48LQFP |

| EFM32-TG230F32-SK | IC MICRO KIT GECKO 64QFN |

| EFM32-TG210F32-SK | IC MICRO KIT GECKO 32QFN |

| 1267 X 6" | TAPE ALUMINUM FOIL 6" X 1FT |

| 7810 0.25MM | ECAP COND PAD .25MM 7.7" X 10" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EFM32TG822F32-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 32KB FLASH 48TQFP |

| EFM32TG822F8 | 功能描述:ARM微控制器 - MCU 8KB Flash 2KB RAM RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT |

| EFM32TG822F8-QFP48 | 制造商:Energy Micro AS 功能描述:TINY GECKO MCU - Tape and Reel 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 8KB FLASH 48TQFP |

| EFM32TG822F8-QFP48T | 制造商:Energy Micro AS 功能描述:32 BIT ARM MPU, TINY GECKO - Trays |

| EFM32TG822F8-QFP48-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 8KB FLASH 48TQFP |

发布紧急采购,3分钟左右您将得到回复。